小芯片項目推動標準和新生態系統

發布時間:2018/12/11 10:28:33 訪問次數:20331

- 51電子網公益庫存:

- 74HC00

- ADG442BR

- AO3418

- ADUM1410ARWZ

- ADUM1410BRWZ

- BA592

- BA595

- BLM15BB750SN1

- C1005X5R1E104KT

- AD5313ARUZ

- AD5313BRUZ

- AD5443YRM

- AD5443YRMZ

- GRM1555C1H101J

- GRM1555C1H330JZ01D

- GRM155R61E104KA87D

- GRM155R61E105KA12D

- L4960

- LBAT54LT1G

- LTC2635HUD-HMI8#PBF

沒有一個封裝類型可以滿足所有的要求,所以客戶可能會使用許多技術。“有很多選項,每個異構集成將有它的位置,”techsearch international的總裁jan vardaman說“不可能一刀切。”

小芯片成為主流選擇在技術還面臨一些挑戰,“這在幻燈片上看起來很容易,”vardaman說,“但要真正成為產品更具有挑戰性。好的設計和高收益是成功的關鍵。”

并不是所有的小芯片方法都是類似的,每個分類都有一個不同的變數。另外,小芯片的市場有點兒混亂,它是否能兌現承諾現在還不清楚。

為了幫助行業取得領先地位,我們先帶你看一看各種各樣的小芯片技術吧!

小芯片的挑戰

小芯片的概念并不是新的。該技術可以追溯到20世紀80年代,那時行業開發出多芯片模塊(mcms)。在mcms,需要集成多個芯片并將它們組成一個模塊。http://xhwydz03.51dzw.com

當時mcms被歸類到高端系統主機。對于其他系統,行業采用商業封裝。總之,封裝看起來更像是一個事后補救的辦法。

最近這些開始改變了,行業意識到在每一個節點的微縮成本高漲和越來越復雜了。今天只有少數精英能夠承受先進節點的成本,例如一個28納米的設計費用是5130萬美元,可是到了7納米芯片這個設計費用就要上升到2.978億美元(數據來源:《國際商業戰略》(ibs))。

剛剛過了千禧年,業界開始尋找替代方案,這個替代方案就是先進封裝。與在平面芯片微縮尺寸不同,先進封裝的方式是向垂直方向走。

這并不是說業界停止了微縮,相反業界正在加緊進行10納米/7納米甚至5納米的研發,另外一方面,先進封裝已經在一些利基市場以有限的形式應用了許多年。

對許多客戶來說,先進封裝的出現成為了與微縮平行的一種技術路線和替代,特別是在一些前沿的設計中,使他們有了多種選擇方案。例如業界已經量產的2.5d封裝技術。在2.5d技術中,芯片被堆積在封裝基板上面,結合使用了直通硅晶穿孔(tsvs)技術。該基板作為芯片和電路板之間的橋梁,它提供了更多的i/o接口和帶寬。

幾年前又出現了fan-out。fan-out的裸片被堆積起來但仍在晶片上。

但在不久前,小芯片的方式出現了。這是一種不同的器件搭建方式。用soc芯片可以搭建一個cpu,加上額外的100個ip模塊在同一個芯片上。設計被微縮移動到下一個節點的規模,這是一個非常昂貴的工藝。

利用小芯片模型,那些100個ip被固化為更小的裸片或小芯片,在理論上,你可以從各種ic供應商那里得到一個很大的小芯片目錄。然后,你可以混合和匹配他們建立一個系統。小芯片可以是不同的工藝節點制造,可用于不同的設計。

這就是chips項目和其他廠家努力要完成的事情。“例如,你買的許多ip核是很貴的且來自不同廠商,不可能用一個工藝節點制造,它可能是另一個工藝制造的,”某模擬/射頻設計公司、也是darpa的chips項目成員的首席技術官craig hornbuckle說,“在chips,你可以把一個集成的器件放在一起組成你所需要的系統,這是一個優勢。”

這種方法可以解決其他問題。“先進的工藝節點都是面向數字電路,他們不是面向高性能模擬電路。作為設計師,我們熟悉這些應用,但它是具有挑戰性的且需要很長的時間。(用小芯片),你可以使用一個特定的節點面對一個應用,”hornbuckle說。

還有其他一些好處。“小芯片的一個主要目的是找到一個選項來縮短在面向soc設計的考慮時的設計周期/成本,假設有相同的性能,” lam research的先進封裝副總裁choon lee說,“小芯片的概念可以被采用到功能優先的應用中,例如,軍事或者航空航天領域。”

要做到這一點還面臨一些挑戰,其中有:

■ 眼下還沒有標準的方法貼裝或堆積小芯片;http://xhwydz03.51dzw.com

■ 裸片到裸片的互連方案很昂貴;

■ 設計和制造之間還有缺口,例如如何驗證和測試小芯片;

■ 有一點還不是很清楚:誰將負責這些小芯片,一旦它們被制造出來交給集成商和封裝廠以后。

很明顯,設計和測試的考慮是關鍵。“小芯片設計應當包括圍繞有源芯片的系統設計中。它需要通過互連/功能性測試來測試外部世界與小芯片以及小芯片到主芯片的兼容性。這些還涉及模塊產量的問題。”lee說。

其他人也同意這一點。“小芯片在理論上看是偉大的,但真要到推翻神像般的soc模型還有許多挑戰要克服,”西門子mentor的drc應用市場主任john ferguson說。“也許單獨的小芯片與其對應的用單一工藝制造的嵌入式ip成本會下來,但還有其他成本和風險。在研發和專用pdks的支持下,代工廠實現socs的設計相對容易和低風險。當我們走近一個獨立的小芯片設計團隊(在公司內或第三方團隊),會發現組合小芯片到一個單獨封裝的設計到制造流程仍處在一個嬰兒期階段。”

部分原因是小芯片技術隱含了多重的制造和供應鏈。這使得它很難獲取一個處方能確保所有的小芯片能正確獨立地工作,特別是在和其他芯片處在一個封裝的情況下。

“雖然小芯片在理論上可以被重用在多重設計中,每個小芯片將有其自身的局限性如何以及在何處可以使用,這取決于具體的實現,”ferguson說。“裸片如何互相作用將大量決定它們如何在一個給定的環境內工作。它們是通過焊料球連接或者直接壓焊?后端進出是否需要tsvs?哪一種測試協議被內置在小芯片中?”

正如任何芯片或封裝,產量是關鍵。“集成小芯片到一個系統級封裝(sip)中將驅動越來越高密度的互連。是否使用硅基板組裝小芯片,還是硅橋,或高密度的fan-out,小芯片的趨勢是越來越小、間距越來越精細和微凸起,” kla-tencor的高級營銷總監stephen hiebert說。“這些微凸起互連必須是無缺陷的,必須要求100%的篩選檢查以確保無殺手缺陷。另外,硅基板、硅橋以及無硅分布層必須滿足高質量和高產量的需求,這是因為被安裝的ic容量的累積價值所致。“

另一個問題是誰將負責一個給定的項目。“小芯片可能會來自一個總包的idm廠商,或一個能夠控制生產小芯片、封裝和安裝小芯片到系統的代工廠,”applied materials的封裝副總裁nirmalyamaity說,“這避免了潛在的從不同供應商采購小芯片帶來的質量和互換性的差異問題,這可能影響系統的功能。單一的總包供應商也可以避免多供應商帶來的交貨延遲和復雜的供應鏈。例如,如果多供應商和服務商被引入,誰負責系統產量和功能?如何測試元件和子系統以確保它們在進入生產線之前是合格的?”

成本當然是至關重要的因素。“資本支出和擁有成本的敏感性也是一個限制因素,”maity說,“這些因素驅動需求有成本效益的和創新性方案。”

商業供應商

marvell和kandou bus是第一個跳轉到小芯片概念的公司。2016年,它們宣布了一項協議,marvell將使用kandou的芯片到芯片互連技術將多個芯片連接在一起。

andou正在開發一個適于中小企業的生態系統,并已同意放棄其ip給其它人以啟動這個方法。marvell正在基于kandou的互連技術構建一個轉換器。

“如果你想把所有東西都集成在一個芯片上,它需要很長的時間。如果你想使用先進的工藝,它的成本會更高,”kandou bus 的首席執行官amin shokrollahi說。

降低開發新的芯片的成本對一些市場來說至關重要,“我們用小芯片看到的是一個巨大的蛻變,”shokrollahi說。“這是一支只做一件事的小公司的軍隊,僅僅一件事而已,這使他們能夠快速進入市場。所以,如果你想在一個小公司開發一個網絡接口卡,他們能結合自己的技術和一些其他的東西,很快得到一個工作原型機。最大的轉變是有了小芯片,小公司也可以負擔得起創新。”

去年,初創公司zglue宣布啟動一項在封裝中堆疊芯片的技術,zglue沒有自己的芯片。相反,它正在積累來自第三方的芯片貨架籌碼。

第三方的芯片已經在代工廠生產并完成了芯片級封裝,公司也準備支持已知合格芯片(kgd)和觸點陣列封裝(lgas)。

zglue提供的是一個專有平臺和模塊,以及有源封裝基板。模塊的基礎由pcb板和電路組成。模塊本身是一個bga封裝的形式。

在平臺或模塊的內部,小芯片被放到一個類似網狀的織物上,這個織物是一個可編程基板。130納米的基板是在臺積電代工制造的,由ase為zglue提供裝配工藝。“我們有一個從不同供應商得到晶片級芯片級封裝的機制,并且不施加任何限制就像我們使用它們那樣,”zglue的技術執行官jawadnasrullah說。“(有源基板)是一種分布式微柱的表面,有點像魔術帖,你可以利用表面貼裝技術將芯片放置在上面。基于基板和實際生產的,你可以為它做某些調整。所有的連接由軟件操作,除了在某些部位基本上沒有硬件的參與。”http://xhwydz03.51dzw.com

zglue正專注于連接領域的某些特殊應用,如藍牙、窄帶iot、wifi和可穿戴設備等。一年前zglue已經有了第三方提供的10個小芯片組合。現在它已經有了來自30-40個供應商的100個小芯片組合,并計劃在未來有500個小芯片組合。在公司的組合里,adi, dialog, macronix and vishay 都是小芯片的供應商。

darpa的方法

2016年,darpa為它的chips項目向外部公司招標。當時目標是(現在依然是)為小芯片設計一個模塊設計和制造的流程。darpa也計劃開發一個大的第三方小芯片目錄以滿足商業和軍事應用。總之,chips流程希望能減少70%的設計成本和周轉時間。

chips項目2017年正式開始,項目有各種承包商/子承包商——制造廠商(英特爾,northrop,micross和ucla);小芯片開發商(ferric,jariet, micron, synopsys, and university of michigan);以及eda工具開發商(cadence and georgia institute of technology)。

chips是darpa在電子復興倡議(eri)下的幾個項目之一,eri是一個五年期的,包含15億美元投資的電子行業創新振興計劃。

“(用chips)我們試圖創建一個芯片設計的新方法,”darpa的olofsson說,“我們必須重建生態系統。我們必須重建我們設計產品的方式。我們必須發明新的制造技術。”

darpa正在研究幾大塊拼圖來實現它的目標,包括為小芯片規劃標準,為業界實現一個“即插即用”的模型,設計更快的傳輸接口(serdes)技術,為芯片與芯片連接開發低成本的基板/橋。darpa也在開發新的拾取-貼裝(pick-and-place)系統,使得小芯片可以高速地貼裝到封裝上。

標準是關鍵。“一旦我們有了標準,你可以想像在美國任何一家供應商設計許多的小芯片并出售它們。因此系統集成商可以構建復雜的系統,”olofsson說。

chips在標準戰線上正在取得進展。作為它的一部分,英特爾正在頒發許可使用它的先進接口總線(aib)。總線可以處理高帶寬,以及在一個封裝里芯片到芯片之間的通訊。

作為chips的一部分,英特爾開啟了aib發起人組織,它將無版權費地提供技術。隨著時間的推移,英特爾還計劃組建一個aib財團。

作為chips會員,英特爾還提供它的硅橋技術,這是一種可替代硅基板的技術。英特爾的技術,也被稱為嵌入式多芯片互連橋(emib),利用一塊硅在一個封裝內連接芯片到另一個芯片。此外,會員也可以利用傳統的硅基板互連技術。

目前先進封裝和利用“小芯片”構建系統的勢頭正在增強,但從市場的角度看技術上還存在一些挑戰。

一個由darpa領導的機構、marvell和zglue以及其他一些公司正在研發“小芯片”(chiplet)技術,這是在同一個封裝或系統里集成多個裸片的不同方式。美國國防部下屬的國防高級研究計劃局(darpa)希望能為這個小芯片項目推動標準和新的生態系統,這個計劃被稱為“公共異構集成和ip重用戰略”(common heterogeneous integration and ip reuse strategies ,簡稱為chips)。波音, cadence, lockheed, 英特爾, northrop grumman, 美光, synopsys 和其他一些公司正在加入到這一項目,其目標應用是商業、軍事和航空航天領域。

小芯片有幾種技術途徑。基本思路是建立一個模塊化芯片、或小芯片的庫菜單,利用裸片到裸片的互連方案連接小芯片到一個封裝。從理論上講,小芯片技術是一個快速和低成本的方式,可將第三方芯片,例如,i/o、存儲器和處理器核,集成到一個封裝里。

“利用小芯片技術,你可以像legos那樣真正開始構建系統,”darpa微系統技術辦公室項目主管andreas olofsson說。“如果我們擁有成千上百個微小的小芯片在架子上,我們就可以討論在幾天里或幾周內做出體現最高水平的設計。”

至今行業已經開發出某些利用類似小芯片的封裝技術,至少是在有限的體積內。但我們的目標是使小芯片技術成為一個主流選擇,為了這個目標,行業還需要諸多標準、廣泛的小芯片陣列、設計工具和新的制造技術。

無論怎樣,類似小芯片那樣的多芯片封裝市場越來越熱,它們有可能替代傳統的芯片微縮技術。在微縮領域,通過縮小芯片的特征尺寸可以使芯片體積越來越小,功能越來越多。但是芯片的微縮成本越來越大,每個節點帶來的收益也開始打折。http://xhwydz03.51dzw.com

另一個享受微縮帶來的收益的方式是集成多芯片、不同功能的芯片在先進封裝里,某些時候被稱為異構集成。2.5d/3d、fan-out和系統級封裝(sips),都是封裝異構集成的常見例子。但小芯片卻是另一種選擇。文章出自:智慧產品圈:(原文譯自:semiconductor engineering by mark lapedus,謝謝。)

- 51電子網公益庫存:

- 74HC00

- ADG442BR

- AO3418

- ADUM1410ARWZ

- ADUM1410BRWZ

- BA592

- BA595

- BLM15BB750SN1

- C1005X5R1E104KT

- AD5313ARUZ

- AD5313BRUZ

- AD5443YRM

- AD5443YRMZ

- GRM1555C1H101J

- GRM1555C1H330JZ01D

- GRM155R61E104KA87D

- GRM155R61E105KA12D

- L4960

- LBAT54LT1G

- LTC2635HUD-HMI8#PBF

沒有一個封裝類型可以滿足所有的要求,所以客戶可能會使用許多技術。“有很多選項,每個異構集成將有它的位置,”techsearch international的總裁jan vardaman說“不可能一刀切。”

小芯片成為主流選擇在技術還面臨一些挑戰,“這在幻燈片上看起來很容易,”vardaman說,“但要真正成為產品更具有挑戰性。好的設計和高收益是成功的關鍵。”

并不是所有的小芯片方法都是類似的,每個分類都有一個不同的變數。另外,小芯片的市場有點兒混亂,它是否能兌現承諾現在還不清楚。

為了幫助行業取得領先地位,我們先帶你看一看各種各樣的小芯片技術吧!

小芯片的挑戰

小芯片的概念并不是新的。該技術可以追溯到20世紀80年代,那時行業開發出多芯片模塊(mcms)。在mcms,需要集成多個芯片并將它們組成一個模塊。http://xhwydz03.51dzw.com

當時mcms被歸類到高端系統主機。對于其他系統,行業采用商業封裝。總之,封裝看起來更像是一個事后補救的辦法。

最近這些開始改變了,行業意識到在每一個節點的微縮成本高漲和越來越復雜了。今天只有少數精英能夠承受先進節點的成本,例如一個28納米的設計費用是5130萬美元,可是到了7納米芯片這個設計費用就要上升到2.978億美元(數據來源:《國際商業戰略》(ibs))。

剛剛過了千禧年,業界開始尋找替代方案,這個替代方案就是先進封裝。與在平面芯片微縮尺寸不同,先進封裝的方式是向垂直方向走。

這并不是說業界停止了微縮,相反業界正在加緊進行10納米/7納米甚至5納米的研發,另外一方面,先進封裝已經在一些利基市場以有限的形式應用了許多年。

對許多客戶來說,先進封裝的出現成為了與微縮平行的一種技術路線和替代,特別是在一些前沿的設計中,使他們有了多種選擇方案。例如業界已經量產的2.5d封裝技術。在2.5d技術中,芯片被堆積在封裝基板上面,結合使用了直通硅晶穿孔(tsvs)技術。該基板作為芯片和電路板之間的橋梁,它提供了更多的i/o接口和帶寬。

幾年前又出現了fan-out。fan-out的裸片被堆積起來但仍在晶片上。

但在不久前,小芯片的方式出現了。這是一種不同的器件搭建方式。用soc芯片可以搭建一個cpu,加上額外的100個ip模塊在同一個芯片上。設計被微縮移動到下一個節點的規模,這是一個非常昂貴的工藝。

利用小芯片模型,那些100個ip被固化為更小的裸片或小芯片,在理論上,你可以從各種ic供應商那里得到一個很大的小芯片目錄。然后,你可以混合和匹配他們建立一個系統。小芯片可以是不同的工藝節點制造,可用于不同的設計。

這就是chips項目和其他廠家努力要完成的事情。“例如,你買的許多ip核是很貴的且來自不同廠商,不可能用一個工藝節點制造,它可能是另一個工藝制造的,”某模擬/射頻設計公司、也是darpa的chips項目成員的首席技術官craig hornbuckle說,“在chips,你可以把一個集成的器件放在一起組成你所需要的系統,這是一個優勢。”

這種方法可以解決其他問題。“先進的工藝節點都是面向數字電路,他們不是面向高性能模擬電路。作為設計師,我們熟悉這些應用,但它是具有挑戰性的且需要很長的時間。(用小芯片),你可以使用一個特定的節點面對一個應用,”hornbuckle說。

還有其他一些好處。“小芯片的一個主要目的是找到一個選項來縮短在面向soc設計的考慮時的設計周期/成本,假設有相同的性能,” lam research的先進封裝副總裁choon lee說,“小芯片的概念可以被采用到功能優先的應用中,例如,軍事或者航空航天領域。”

要做到這一點還面臨一些挑戰,其中有:

■ 眼下還沒有標準的方法貼裝或堆積小芯片;http://xhwydz03.51dzw.com

■ 裸片到裸片的互連方案很昂貴;

■ 設計和制造之間還有缺口,例如如何驗證和測試小芯片;

■ 有一點還不是很清楚:誰將負責這些小芯片,一旦它們被制造出來交給集成商和封裝廠以后。

很明顯,設計和測試的考慮是關鍵。“小芯片設計應當包括圍繞有源芯片的系統設計中。它需要通過互連/功能性測試來測試外部世界與小芯片以及小芯片到主芯片的兼容性。這些還涉及模塊產量的問題。”lee說。

其他人也同意這一點。“小芯片在理論上看是偉大的,但真要到推翻神像般的soc模型還有許多挑戰要克服,”西門子mentor的drc應用市場主任john ferguson說。“也許單獨的小芯片與其對應的用單一工藝制造的嵌入式ip成本會下來,但還有其他成本和風險。在研發和專用pdks的支持下,代工廠實現socs的設計相對容易和低風險。當我們走近一個獨立的小芯片設計團隊(在公司內或第三方團隊),會發現組合小芯片到一個單獨封裝的設計到制造流程仍處在一個嬰兒期階段。”

部分原因是小芯片技術隱含了多重的制造和供應鏈。這使得它很難獲取一個處方能確保所有的小芯片能正確獨立地工作,特別是在和其他芯片處在一個封裝的情況下。

“雖然小芯片在理論上可以被重用在多重設計中,每個小芯片將有其自身的局限性如何以及在何處可以使用,這取決于具體的實現,”ferguson說。“裸片如何互相作用將大量決定它們如何在一個給定的環境內工作。它們是通過焊料球連接或者直接壓焊?后端進出是否需要tsvs?哪一種測試協議被內置在小芯片中?”

正如任何芯片或封裝,產量是關鍵。“集成小芯片到一個系統級封裝(sip)中將驅動越來越高密度的互連。是否使用硅基板組裝小芯片,還是硅橋,或高密度的fan-out,小芯片的趨勢是越來越小、間距越來越精細和微凸起,” kla-tencor的高級營銷總監stephen hiebert說。“這些微凸起互連必須是無缺陷的,必須要求100%的篩選檢查以確保無殺手缺陷。另外,硅基板、硅橋以及無硅分布層必須滿足高質量和高產量的需求,這是因為被安裝的ic容量的累積價值所致。“

另一個問題是誰將負責一個給定的項目。“小芯片可能會來自一個總包的idm廠商,或一個能夠控制生產小芯片、封裝和安裝小芯片到系統的代工廠,”applied materials的封裝副總裁nirmalyamaity說,“這避免了潛在的從不同供應商采購小芯片帶來的質量和互換性的差異問題,這可能影響系統的功能。單一的總包供應商也可以避免多供應商帶來的交貨延遲和復雜的供應鏈。例如,如果多供應商和服務商被引入,誰負責系統產量和功能?如何測試元件和子系統以確保它們在進入生產線之前是合格的?”

成本當然是至關重要的因素。“資本支出和擁有成本的敏感性也是一個限制因素,”maity說,“這些因素驅動需求有成本效益的和創新性方案。”

商業供應商

marvell和kandou bus是第一個跳轉到小芯片概念的公司。2016年,它們宣布了一項協議,marvell將使用kandou的芯片到芯片互連技術將多個芯片連接在一起。

andou正在開發一個適于中小企業的生態系統,并已同意放棄其ip給其它人以啟動這個方法。marvell正在基于kandou的互連技術構建一個轉換器。

“如果你想把所有東西都集成在一個芯片上,它需要很長的時間。如果你想使用先進的工藝,它的成本會更高,”kandou bus 的首席執行官amin shokrollahi說。

降低開發新的芯片的成本對一些市場來說至關重要,“我們用小芯片看到的是一個巨大的蛻變,”shokrollahi說。“這是一支只做一件事的小公司的軍隊,僅僅一件事而已,這使他們能夠快速進入市場。所以,如果你想在一個小公司開發一個網絡接口卡,他們能結合自己的技術和一些其他的東西,很快得到一個工作原型機。最大的轉變是有了小芯片,小公司也可以負擔得起創新。”

去年,初創公司zglue宣布啟動一項在封裝中堆疊芯片的技術,zglue沒有自己的芯片。相反,它正在積累來自第三方的芯片貨架籌碼。

第三方的芯片已經在代工廠生產并完成了芯片級封裝,公司也準備支持已知合格芯片(kgd)和觸點陣列封裝(lgas)。

zglue提供的是一個專有平臺和模塊,以及有源封裝基板。模塊的基礎由pcb板和電路組成。模塊本身是一個bga封裝的形式。

在平臺或模塊的內部,小芯片被放到一個類似網狀的織物上,這個織物是一個可編程基板。130納米的基板是在臺積電代工制造的,由ase為zglue提供裝配工藝。“我們有一個從不同供應商得到晶片級芯片級封裝的機制,并且不施加任何限制就像我們使用它們那樣,”zglue的技術執行官jawadnasrullah說。“(有源基板)是一種分布式微柱的表面,有點像魔術帖,你可以利用表面貼裝技術將芯片放置在上面。基于基板和實際生產的,你可以為它做某些調整。所有的連接由軟件操作,除了在某些部位基本上沒有硬件的參與。”http://xhwydz03.51dzw.com

zglue正專注于連接領域的某些特殊應用,如藍牙、窄帶iot、wifi和可穿戴設備等。一年前zglue已經有了第三方提供的10個小芯片組合。現在它已經有了來自30-40個供應商的100個小芯片組合,并計劃在未來有500個小芯片組合。在公司的組合里,adi, dialog, macronix and vishay 都是小芯片的供應商。

darpa的方法

2016年,darpa為它的chips項目向外部公司招標。當時目標是(現在依然是)為小芯片設計一個模塊設計和制造的流程。darpa也計劃開發一個大的第三方小芯片目錄以滿足商業和軍事應用。總之,chips流程希望能減少70%的設計成本和周轉時間。

chips項目2017年正式開始,項目有各種承包商/子承包商——制造廠商(英特爾,northrop,micross和ucla);小芯片開發商(ferric,jariet, micron, synopsys, and university of michigan);以及eda工具開發商(cadence and georgia institute of technology)。

chips是darpa在電子復興倡議(eri)下的幾個項目之一,eri是一個五年期的,包含15億美元投資的電子行業創新振興計劃。

“(用chips)我們試圖創建一個芯片設計的新方法,”darpa的olofsson說,“我們必須重建生態系統。我們必須重建我們設計產品的方式。我們必須發明新的制造技術。”

darpa正在研究幾大塊拼圖來實現它的目標,包括為小芯片規劃標準,為業界實現一個“即插即用”的模型,設計更快的傳輸接口(serdes)技術,為芯片與芯片連接開發低成本的基板/橋。darpa也在開發新的拾取-貼裝(pick-and-place)系統,使得小芯片可以高速地貼裝到封裝上。

標準是關鍵。“一旦我們有了標準,你可以想像在美國任何一家供應商設計許多的小芯片并出售它們。因此系統集成商可以構建復雜的系統,”olofsson說。

chips在標準戰線上正在取得進展。作為它的一部分,英特爾正在頒發許可使用它的先進接口總線(aib)。總線可以處理高帶寬,以及在一個封裝里芯片到芯片之間的通訊。

作為chips的一部分,英特爾開啟了aib發起人組織,它將無版權費地提供技術。隨著時間的推移,英特爾還計劃組建一個aib財團。

作為chips會員,英特爾還提供它的硅橋技術,這是一種可替代硅基板的技術。英特爾的技術,也被稱為嵌入式多芯片互連橋(emib),利用一塊硅在一個封裝內連接芯片到另一個芯片。此外,會員也可以利用傳統的硅基板互連技術。

目前先進封裝和利用“小芯片”構建系統的勢頭正在增強,但從市場的角度看技術上還存在一些挑戰。

一個由darpa領導的機構、marvell和zglue以及其他一些公司正在研發“小芯片”(chiplet)技術,這是在同一個封裝或系統里集成多個裸片的不同方式。美國國防部下屬的國防高級研究計劃局(darpa)希望能為這個小芯片項目推動標準和新的生態系統,這個計劃被稱為“公共異構集成和ip重用戰略”(common heterogeneous integration and ip reuse strategies ,簡稱為chips)。波音, cadence, lockheed, 英特爾, northrop grumman, 美光, synopsys 和其他一些公司正在加入到這一項目,其目標應用是商業、軍事和航空航天領域。

小芯片有幾種技術途徑。基本思路是建立一個模塊化芯片、或小芯片的庫菜單,利用裸片到裸片的互連方案連接小芯片到一個封裝。從理論上講,小芯片技術是一個快速和低成本的方式,可將第三方芯片,例如,i/o、存儲器和處理器核,集成到一個封裝里。

“利用小芯片技術,你可以像legos那樣真正開始構建系統,”darpa微系統技術辦公室項目主管andreas olofsson說。“如果我們擁有成千上百個微小的小芯片在架子上,我們就可以討論在幾天里或幾周內做出體現最高水平的設計。”

至今行業已經開發出某些利用類似小芯片的封裝技術,至少是在有限的體積內。但我們的目標是使小芯片技術成為一個主流選擇,為了這個目標,行業還需要諸多標準、廣泛的小芯片陣列、設計工具和新的制造技術。

無論怎樣,類似小芯片那樣的多芯片封裝市場越來越熱,它們有可能替代傳統的芯片微縮技術。在微縮領域,通過縮小芯片的特征尺寸可以使芯片體積越來越小,功能越來越多。但是芯片的微縮成本越來越大,每個節點帶來的收益也開始打折。http://xhwydz03.51dzw.com

另一個享受微縮帶來的收益的方式是集成多芯片、不同功能的芯片在先進封裝里,某些時候被稱為異構集成。2.5d/3d、fan-out和系統級封裝(sips),都是封裝異構集成的常見例子。但小芯片卻是另一種選擇。文章出自:智慧產品圈:(原文譯自:semiconductor engineering by mark lapedus,謝謝。)

熱門點擊

熱門點擊

- C++20

- 下一代量子互聯網

- 集成電路發展歷程及未來趨勢

- 半導體行業2018年并購案例解讀

- Imagination:AI和GPU創新技術和產品

- 2019年大AI科技趨勢

- MOS管驅動電路詳解

- 2019年十大“驚人預言”

- “世界最具影響力十大華商人物”

- 三星發展7納米至3納米先進制程

推薦電子資訊

推薦電子資訊

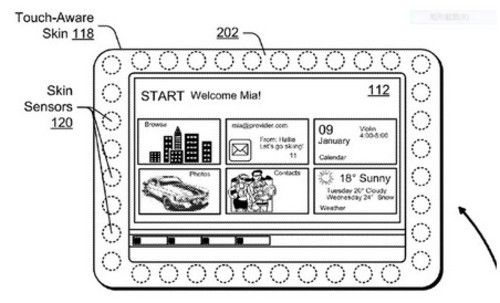

- 微軟新專利:皮膚感應邊框

- 該專利名為“基于抓握的裝置適應(Grip-Based&... [詳細]

公網安備44030402000607

公網安備44030402000607