5103310-5下降沿觸發的kK觸發器模塊

發布時間:2020/1/21 21:13:10 訪問次數:2091

5103310-5例5.5.3給出了一個下降沿觸發的k`k觸發器模塊,它應用了另一種描述方法。根據jk觸發器的功能表,它使用多路分支語句case進行描述。這里,將輸人變量j、k拼接起來成為一個2位二進制變量({j,k}),它的值可能是二進制數00、01、10、11,case語句后面的4條分支語句正好說明了在時鐘信號cp下降沿作用后,觸發器的次態。注意,case語句中所列出的各個條件是不存在優先權差別的,這種語句是直接從功能表進行電路描述的常用方法。

例5,4.3

//functional description of jk~nip~n。p (see fig・ 5・3,7)

m,odule jk~ff(q,qn。t,j,Κ,cp);

output q,qnot;

nnput j,k,cp;

reg q;

assign qnot = ~ q ;

always@(negedge cp)

case({j,k}) //switch based on concatenation of j and k signals

2i b00: q (= q;

2’b01: q <= 1i bo;

2’b10: q (= 1i b1;

2i b11:q(=~q;

endcase

endmodule

5.4.4 在verilog中,initial語句和always語句的主要區別是什么,鎖存器和觸發器.

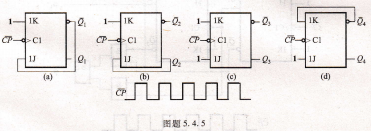

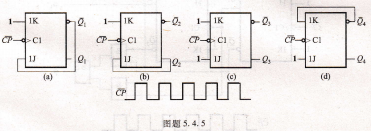

5.4.5 邏輯電路如圖題5.4.5所示,已知cp和i的波形,試畫出0i和q2的波形。觸發器的初始狀態均為0。

5.4.7 邏輯電路如圖題5.4.7所示,已知cp和a的波形,畫出觸發器q端的波形,設觸發器的初始狀態為0。

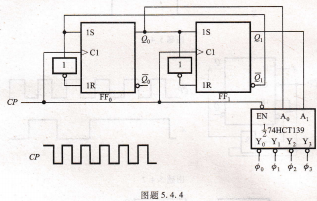

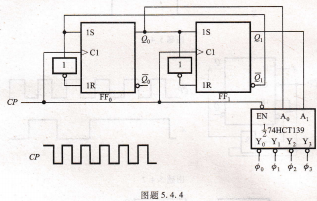

5.4.8 兩相脈沖產生電路如圖題5.4.8所示,試畫出在cp作用下φl、φ2的波形,并說明φl和φ2的時間關系,各觸發器的初始狀態為0。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

5103310-5例5.5.3給出了一個下降沿觸發的k`k觸發器模塊,它應用了另一種描述方法。根據jk觸發器的功能表,它使用多路分支語句case進行描述。這里,將輸人變量j、k拼接起來成為一個2位二進制變量({j,k}),它的值可能是二進制數00、01、10、11,case語句后面的4條分支語句正好說明了在時鐘信號cp下降沿作用后,觸發器的次態。注意,case語句中所列出的各個條件是不存在優先權差別的,這種語句是直接從功能表進行電路描述的常用方法。

例5,4.3

//functional description of jk~nip~n。p (see fig・ 5・3,7)

m,odule jk~ff(q,qn。t,j,Κ,cp);

output q,qnot;

nnput j,k,cp;

reg q;

assign qnot = ~ q ;

always@(negedge cp)

case({j,k}) //switch based on concatenation of j and k signals

2i b00: q (= q;

2’b01: q <= 1i bo;

2’b10: q (= 1i b1;

2i b11:q(=~q;

endcase

endmodule

5.4.4 在verilog中,initial語句和always語句的主要區別是什么,鎖存器和觸發器.

5.4.5 邏輯電路如圖題5.4.5所示,已知cp和i的波形,試畫出0i和q2的波形。觸發器的初始狀態均為0。

5.4.7 邏輯電路如圖題5.4.7所示,已知cp和a的波形,畫出觸發器q端的波形,設觸發器的初始狀態為0。

5.4.8 兩相脈沖產生電路如圖題5.4.8所示,試畫出在cp作用下φl、φ2的波形,并說明φl和φ2的時間關系,各觸發器的初始狀態為0。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607