CL6807是一款高側電流感應的高亮度LED驅動控制器,設計運用于高效驅動由高于LED正向導通電壓的電源供電的單個或多個串聯LED。該裝置的運作是在6V到35V之間,提供了一個外部可調的高達1A的輸出電流。根據電力供應的電壓和外部元件,可以提供高達25瓦的輸出功率。

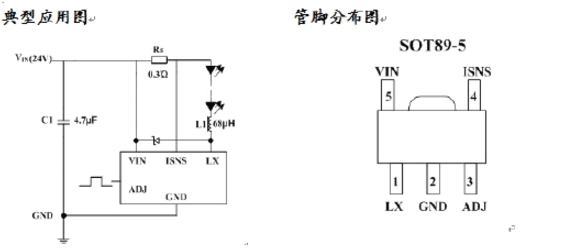

CL6807包括輸出開關和一個高側的輸出電流傳感電路, 可利用外部電阻器來設定的平均輸出電流或由精心設計的直流電壓或PWM信號來加載ADJ腳來調節輸出電流。在ADJ腳上加低于0.5V的電壓將關斷輸出電流和開關動作,使該芯片進入低功耗待機狀態。CL6807的封裝為SOT89-5。

特點:

◆ 極少的外圍器件數

◆ 寬輸入電壓范圍:6V至35V

◆ 高達1A的輸出電流

◆ 開關控制及亮度的直流電壓控制和PWM控制由單腳實現

◆ 輸出電流準確性可達±5%

◆ 內建的LED開路保護

◆高達95%的效率

◆高測電流感應

◆遲滯控制,無需補償

應用:

◆LED替換低壓鹵素燈應用

◆汽車照明

◆ 低壓照明工業

◆ LED后備照明

◆ 發亮標志

◆ 緊急照明系統

◆ 液晶電視背光

適用了20余年的摩爾定律近年逐漸有了失靈的跡象。從芯片的制造來看,7nm就是硅材料芯片的物理極限。不過據外媒報道,勞倫斯伯克利國家實驗室的一個團隊打破了物理極限,采用碳納米管復合材料將現有最精尖的晶體管制程從14nm縮減到了1nm。那么,為何說7nm就是硅材料芯片的物理極限,碳納米管復合材料又是怎么一回事呢?面對美國的技術突破,中國應該怎么做呢?

XX nm制造工藝是什么概念?

芯片的制造工藝常常用90nm、65nm、40nm、28nm、22nm、14nm來表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm制造工藝。現在的CPU內集成了以億為單位的晶體管,這種晶體管由源極、漏極和位于他們之間的柵極所組成,電流從源極流入漏極,柵極則起到控制電流通斷的作用。

而所謂的XX nm其實指的是,CPU的上形成的互補氧化物金屬半導體場效應晶體管柵極的寬度,也被稱為柵長。

柵長越短,則可以在相同尺寸的硅片上集成更多的晶體管——Intel曾經宣稱將柵長從130nm減小到90nm時,晶體管所占得面積將減小一半;在芯片晶體管集成度相當的情況下,使用更先進的制造工藝,芯片的面積和功耗就越小,成本也越低。

柵長可以分為光刻柵長和實際柵長,光刻柵長則是由光刻技術所決定的。由于在光刻中光存在衍射現象以及芯片制造中還要經歷離子注入、蝕刻、等離子沖洗、熱處理等步驟,因此會導致光刻柵長和實際柵長不一致的情況。另外,同樣的制程工藝下,實際柵長也會不一樣,比如雖然三星也推出了14nm制程工藝的芯片,但其芯片的實際柵長和Intel的14nm制程芯片的實際柵長依然有一定差距。

為什么說7nm是物理極限?

之前解釋了縮短晶體管柵極的長度可以使CPU集成更多的晶體管或者有效減少晶體管的面積和功耗,并削減CPU的硅片成本。正是因此,CPU生產廠商不遺余力地減小晶體管柵極寬度,以提高在單位面積上所集成的晶體管數量。不過這種做法也會使電子移動的距離縮短,容易導致晶體管內部電子自發通過晶體管通道的硅底板進行的從負極流向正極的運動,也就是漏電。而且隨著芯片中晶體管數量增加,原本僅數個原子層厚的二氧化硅絕緣層會變得更薄進而導致泄漏更多電子,隨后泄漏的電流又增加了芯片額外的功耗。

為了解決漏電問題,Intel、IBM等公司可謂八仙過海,各顯神通。比如Intel在其制造工藝中融合了高介電薄膜和金屬門集成電路以解決漏電問題;IBM開發出SOI技術——在在源極和漏極埋下一層強電介質膜來解決漏電問題;此外,還有鰭式場效電晶體技術——借由增加絕緣層的表面積來增加電容值,降低漏電流以達到防止發生電子躍遷的目的......

上述做法在柵長大于7nm的時候一定程度上能有效解決漏電問題。不過,在采用現有芯片材料的基礎上,晶體管柵長一旦低于7nm,晶體管中的電子就很容易產生隧穿效應,為芯片的制造帶來巨大的挑戰。針對這一問題,尋找新的材料來替代硅制作7nm以下的晶體管則是一個有效的解決之法。

1nm制程晶體管還處于處于實驗室階段

碳納米管和近年來非常火爆的石墨烯有一定聯系,零維富勒烯、一維碳納米管、二維石墨烯都屬于碳納米材料家族,并且彼此之間滿足一定條件后可以在形式上轉化。碳納米管是一種具有特殊結構的一維材料,它的徑向尺寸可達到納米級,軸向尺寸為微米級,管的兩端一般都封口,因此它有很大的強度,同時巨大的長徑比有望使其制作成韌性極好的碳纖維。

碳納米管和石墨烯在電學和力學等方面有著相似的性質,有較好的導電性、力學性能和導熱性,這使碳納米管復合材料在超級電容器、太陽能電池、顯示器、生物檢測、燃料電池等方面有著良好的應用前景。此外,摻雜一些改性劑的碳納米管復合材料也受到人們的廣泛關注,例如在石墨烯/碳納米管復合電極上添加CdTe量子點制作光電開關、摻雜金屬顆粒制作場致發射裝置。本次外媒報道的勞倫斯伯克利國家實驗室將現有最精尖的晶體管制程從14nm縮減到了1nm,其晶體管就是由碳納米管摻雜二硫化鉬制作而成。不過這一技術成果僅僅處于實驗室技術突破的階段,目前還沒有商業化量產的能力。至于該項技術將來是否會成為主流商用技術,還有待時間檢驗。

技術進步并不一定帶來商業利益

在過去幾十年中,由于摩爾定律在確實發揮作用,使中國半導體制造技術在追趕西方的過程中始終被國外拉出一段距離。而近年來,芯片制造技術進步放慢,摩爾定律出現失效的客觀現象,對于中國半導體產業追趕西方來說是一大利好。摩爾定律失效,一方面既有技術因素——先進光刻機、刻蝕機等設備以及先進芯片制造技術研發技術難度大、資金要求高......另一方面也有商業上的因素。

在制造工藝到達28nm以前,制造工藝的每一次進步都能使芯片制造廠商獲得巨額利潤。不過,在制造工藝達到14/16nm之后,技術的進步反而會使芯片的成本有所上升——在Intel最先研發出14nm制造工藝時,曾有消息稱其掩膜成本為3億美元。當然,隨著時間的推移和臺積電、三星掌握14/16nm制程,現在的價格應該不會這么貴。但英特爾正在研發的10nm制程,根據Intel官方估算,掩膜成本至少需要10億美元。新制造工藝之所以貴,一方面是貴在新工藝高昂的研發成本和偏低的成品率,另一方面也是因為光刻機、刻蝕機等設備的價格異常昂貴。因此,即便先進制造工藝在技術上成熟了,但由于過于高昂的掩膜成本,會使客戶在選擇采用最先進制造工藝時三思而后行,舉例來說,如果10nm制造工藝芯片的產量低于1000萬片,那么光分攤到每一片芯片上的掩膜成本就高達100美元,按國際通用的低盈利芯片設計公司的定價策略8:20定價法——也就是硬件成本為8的情況下,定價為20,別覺得這個定價高,其實已經很低了,Intel一般定價策略為8:35,AMD歷史上曾達到過8:50......即便不算晶片成本和封測成本,這款10nm CPU的售價也不會低于250美元。同時,相對較少的客戶會導致很難用巨大的產量分攤成本,并最終使企業放緩對先進制造工藝的開發和商業應用。也正是因此,28nm制造工藝被部分業內人士認為是非常有活力的,而且依舊會被持續使用數年。

中國應腳踏實地解決現實問題

對于勞倫斯伯克利國家實驗室將現有最精尖的晶體管制程從14nm縮減到了1nm,國人不必將其看得太重,因為這僅僅是一項在實驗室中的技術突破,哪怕退一步說,該項技術已經成熟且可以商業化,由于其在商業化上的難度遠遠大于Intel正在研發的10nm制造工藝——其成本將高昂地無以復加,這會使采用該技術生產的芯片價格居高不下,這又會導致較少客戶選擇該項技術,進而惡性循環......從商業因素考慮,大部分IC設計公司恐怕依舊會選擇相對成熟,或者稱為相對“老舊”的制造工藝。

對于現在的中國半導體產業而言,與其花費巨大人力物力財力去探索突破7nm物理極限,還不如將有限的人力物力財力用于完善28nm制程工藝的IP庫和實現14nm制造工藝的商業化量產。畢竟,對于國防安全領域而言,現有的制造工藝已完全夠用(美國的很多軍用芯片都還是65nm的),對于商業芯片而言,很多芯片對制程的要求并不高,像工控芯片、汽車電子、射頻等都在使用在一些硬件發燒友看起來顯得老舊的制程,而對于PC和手機、平板電腦的CPU、GPU而言,14nm/16nm的制造工藝已經能將性能和功耗方面的需求平衡的很好。筆者認為,相對于耗費大量資源去研發新材料突破7nm物理極限,還不如腳踏實地地解決現實問題。

公司:深圳市哲瀚電子科技有限公司

聯系人:陳小姐

手機:13714441972

電話:0755-82549527/83259945/13714441972

傳真:0755-83259945

地址:深圳市福田區深圳市福田區華強北街道深南中路3006號佳和大廈3C006