XC7A100T-2CSG324I

XC7A200T-2FBG484I

XC7A200T-2FBG676I

XC6SLX16-2CSG225I

XC6SLX45-2FGG484I

XC6SLX45T-2FGG484I

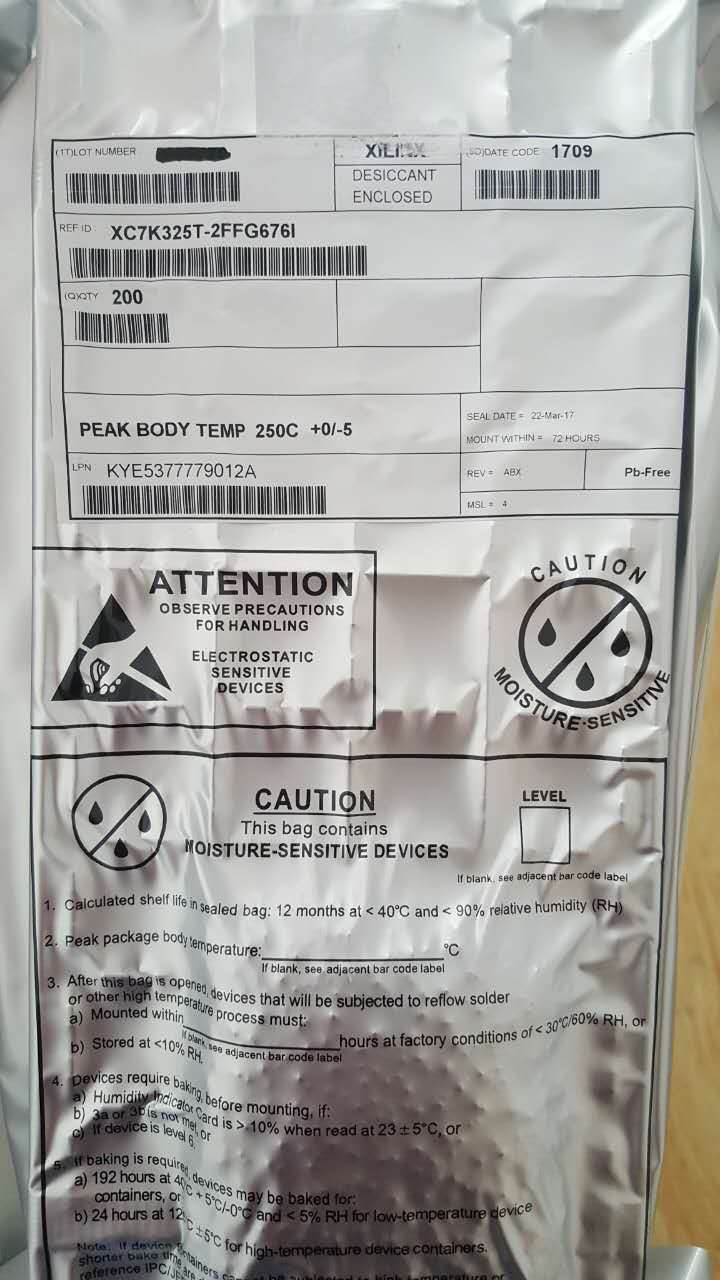

XC7K325T-2FFG676I

XC7K325T-2FFG900I

XCF04SVOG20C

General Description

Xilinx® 7 series FPGAs comprise four FPGA families that address the complete range of system requirements, ranging from low cost, small form factor, cost-sensitive, high-volume applications to ultra high-end connectivity bandwidth, logic capacity, and signal processing capability for the most demanding high-performance applications. The 7 series FPGAs include:

Spartan®-7 Family: Optimized for low cost, lowest power, and high I/O performance. Available in low-cost, very small form-factor packaging for smallest PCB footprint.

• Artix®-7 Family: Optimized for low power applications requiring serial transceivers and high DSP and logic throughput. Provides the lowest total bill of materials cost for high-throughput, cost-sensitive

• Kintex®-7 Family: Optimized for best price-performance with a 2X improvement compared to previous generation, enabling a new class of FPGAs.

• Virtex®-7 Family: Optimized for highest system performance and capacity with a 2X improvement in system performance. Highest capability devices enabled by stacked silicon interconnect (SSI) technology

Summary of 7 Series FPGA Features

• Advanced high-performance FPGA logic based on real 6-input lookup table (LUT) technology configurable as distributed memory.

• 36 Kb dual-port block RAM with built-in FIFO logic for on-chip data buffering.

• High-performance SelectIO™ technology with support for DDR3 interfaces up to 1,866 Mb/s. • High-speed serial connectivity with built-in multi-gigabit transceivers from 600 Mb/s to maximum rates of 6.6 Gb/s up to 28.05 Gb/s, offering a special low-power mode, optimized for chip-to-chip interfaces.

• A user configurable analog interface (XADC), incorporating dual

12-bit 1MSPS analog-to-digital converters with on-chip thermal and

supply sensors.

• DSP slices with 25 x 18 multiplier, 48-bit accumulator, and pre-adder

for high-performance filtering, including optimized symmetric

coefficient filtering.

• Powerful clock management tiles (CMT), combining phase-locked loop (PLL) and mixed-mode clock manager (MMCM) blocks for high precision and low jitter.

• Integrated block for PCI Express® (PCIe), for up to x8 Gen3 Endpoint and Root Port designs.

• Wide variety of configuration options, including support for commodity memories, 256-bit AES encryption with HMAC/SHA-256 authentication, and built-in SEU detection and correction. • Low-cost, wire-bond, lidless flip-chip, and high signal integrity flipchip packaging offering easy migration between family members in the same package. All packages available in Pb-free and selected packages in Pb option.

• Designed for high performance and lowest power with 28 nm,

HKMG, HPL process, 1.0V core voltage process technology and

0.9V core voltage option for even lower power.

深圳市裕碩科技有限公司

聯系人:馬先生

電話銷售:86-0755-82706142/23613962

傳真:86-0755-23613962

Q Q:2028567797/3240702125

微信:2028567797

手機:13378660954

網址:http://yushuollp.51dzw.com