數據列表

2SA2092;

標準包裝 2SA2092TLQ-ND;part_id=657931;ref_supplier_id=846;ref_page_event=Standard Packaging" />

3,000

2SA2092TLQ-ND;part_id=657931;ref_supplier_id=846;ref_page_event=Standard Packaging" />

3,000

包裝 標準卷帶

標準卷帶

類別

分立半導體產品

產品族

晶體管 - 雙極 (BJT) - 單

系列

-

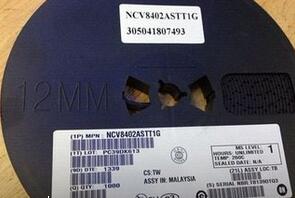

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

規格

晶體管類型

PNP

電流 - 集電極(Ic)(最大值)

1A

電壓 - 集射極擊穿(最大值)

60V

不同Ib,Ic 時的Vce 飽和值(最大值)

500mV @ 50mA,500mA

電流 - 集電極截止(最大值)

1μA(ICBO)

不同Ic,Vce時的 DC 電流增益(hFE)(最小值)

120 @ 100mA,2V

功率 - 最大值

500mW

頻率 - 躍遷

300MHz

工作溫度

150°C(TJ)

安裝類型

表面貼裝

封裝/外殼

SC-96

供應商器件封裝

TSMT3

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

根據國外媒體報道,日前有內部人士表示,三星已經開始計劃在2019

年使用6nm工藝制造移動芯片,而并且將逐漸大幅減少7nm工藝生產

線的投資。據悉,三星計劃在今年安裝兩款全新的光刻機,并且計劃

在2018年繼續追加投資7臺,這樣就將為未來制造工藝的提升提供了

支持,同時還能大幅提高產品的生產效率。

高通剛剛決定放棄將三星作為自己7nm工藝處理器的生產合作伙伴,

目前兩家公司已經開始在10nm工藝的驍龍825處理器進行合作生產。

而高通未來在放棄三星之后,將開始與臺積電合作,因此在7nm工

藝的訂單上,三星目前暫時處于劣勢。

不過這一決定的最終結果就是,三星明年的大部分訂單都將以8nm

的工藝完成,而這一技術基本上是對目前10nm工藝的升級版。盡管

三星將減少投資,但是未來7nm工藝還是非常有可能使用在三星自

家Exynos處理器的生產上。

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

三星的這一舉措具有相當的戰略性,盡管明年的7nm工藝生產會受

到影響,不過從2019年開始,三星將會在與臺積電的競爭中擁有明

顯的優勢。畢竟6nm的制造工藝要比7nm更先進一些。通常來說,

半導體的制造工藝越小,最終產品的功耗和性能上就越優秀。而這

就意味著在2019年,三星將憑借6nm的制造工藝,成為市面上最領

先的芯片制造商。

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝

2SA2092TLQ絕對自己現貨全新進口原裝