繼極為成功的第一代Cyclone®器件之后

系列,Altera®Cyclone II FPGA擴展了低成本FPGA密度最多可容納68,416個邏輯元件(LE),并提供多達622個可用I / O

引腳和高達1.1 Mbit的嵌入式存儲器。 Cyclone II FPGA是

使用臺積電的90nm低k電介質在300mm晶圓上制造

流程以確保快速可用性和低成本。通過最小化硅

Cyclone II器件可以在一個區域內支持復雜的數字系統

芯片的成本可以與ASIC媲美。與其他FPGA供應商不同

降低功耗和性能以降低成本,Altera的

最新一代的低成本FPGA—Cyclone II FPGA,性能提高了60%

性能和90納米功耗的一半

FPGA。 Cyclone II FPGA的低成本和優化功能集使

它們是各種汽車,消費者,

通信,視頻處理,測試和測量等

終端市場解決方案。找到參考設計,系統圖和IP

請訪問www.altera.com,以幫助您快速開發完整的

使用Cyclone II FPGA的最終市場解決方案。

低成本嵌入式處理解決方案

Cyclone II器件支持Nios II嵌入式處理器,該處理器允許

您可以實施定制的嵌入式處理解決方案。旋風II

設備還可以擴展外圍設備,內存,I / O或性能

嵌入式處理器。單個或多個Nios II嵌入式處理器

可以設計到Cyclone II器件中以提供其他功能

協同處理能力,甚至取代現有的嵌入式處理器

你的系統。同時使用Cyclone II和Nios II可以降低成本,

高性能嵌入式處理解決方案,使您能夠

延長產品的生命周期并縮短產品上市時間

標準產品解決方案。

單獨使用Cyclone II FPGA或作為DSP協處理器來改進

數字信號處理(DSP)的性價比

應用程序。您可以實現高性能而低成本的DSP

具有以下Cyclone II功能和設計支持的系統:

■最多150個18×18乘法器

■高達1.1 Mbit的片上嵌入式存儲器

■到外部存儲器的高速接口

■DSP知識產權(IP)內核

■Math Builder Simulink和Matlab的DSP Builder接口

設計環境

■DSP開發套件,Cyclone II版

Cyclone II器件包括針對以下功能而優化的強大FPGA功能集:

低成本應用,包括各種密度,內存,

嵌入式乘法器和打包選項。 Cyclone II器件支持

廣泛的通用外部存儲器接口和I / O協議

低成本應用中所需。 Altera的可參數化IP內核

和合作伙伴可以輕松快捷地使用Cyclone II接口和協議。

■具有4,608至68,416 LE的高密度架構

●M4K嵌入式存儲塊

●高達1.1 Mbit的RAM可用空間而不會減少可用空間

邏輯

●每個塊4,096個存儲位(每個塊4,608個位,包括512個)

奇偶校驗位)

●×1,×2,×4,×8,×9,×16,×18,×32,

和×36

●真正的雙端口(一次讀取和一次寫入,兩次讀取或兩次

寫,×1,×2,×4,×8,×9,×16和×18模式的操作

●字節可在寫入期間屏蔽數據輸入

●最高260 MHz的工作頻率

■嵌入式乘法器

●最多可將150個18-×18位乘法器配置為兩個

獨立的9×9位乘法器,最高250MHz

性能

●可選的輸入和輸出寄存器

■高級I / O支持

●高速差分I / O標準支持,包括LVDS,

RSDS,mini-LVDS,LVPECL,差分HSTL和差分

SSTL

●單端I / O標準支持,包括2.5V和1.8V,

SSTL I和II類,1.8 V和1.5 V HSTL I和II類,3.3 V PCI

和PCI-X 1.0、3.3、2.5、1.8和1.5V LVCMOS以及3.3、2.5,

和1.8V LVTTL

●外圍組件互連特殊興趣小組(PCI)

SIG)PCI本地總線規范,適用于3.3-V的修訂版3.0

對于32位或64位接口,工作頻率為33或66 MHz

●具有外部TI PHY和Altera PCI Express的PCI Express

×1Megacore®功能

●133 MHz PCI-X 1.0規范兼容性

●高速外部存儲器支持,包括DDR,DDR2,

SDR SDRAM和QDRII SRAM受支持

Altera IP MegaCore功能易于使用

●每個I / O元素(IOE)三個專用寄存器:一個輸入

寄存器,一個輸出寄存器和一個輸出使能寄存器

●可編程總線保持功能

●可編程輸出驅動強度功能

●從引腳到IOE或邏輯陣列的可編程延遲

●用于唯一VCCIO和/或VREF組的I / O組分組

設定

●MultiVolt™I / O標準支持1.5、1.8、2.5和

3.3接口

●熱插拔操作支持

●在三態之前和期間,I / O引腳上拉弱

組態

●可編程漏極開路輸出

●系列片上終端

在支持

■靈活的時鐘管理電路

●分層時鐘網絡,性能高達402.5 MHz

●每個設備最多四個PLL提供時鐘乘法和

除法,相移,可編程占空比和外部

時鐘輸出,允許系統級時鐘管理和

偏斜控制

●全局時鐘網絡中最多可驅動16條全局時鐘線

在整個設備上

■設備配置

●快速的串行配置允許配置時間少于

100毫秒

●解壓縮功能允許較小的編程文件

存儲和更快的配置時間

●支持多種配置模式:主動串行,被動

串行和基于JTAG的配置

●支持通過低成本串行配置進行配置

設備

●設備配置支持多種電壓(3.3、2.5,

或1.8 V)

■知識產權

●支持Altera宏功能和Altera MegaCore功能,

和Altera宏功能合作伙伴計劃(AMPPSM)

宏功能支持,適用于廣泛的嵌入式

處理器,片上和片外接口,外圍設備

功能,DSP功能和通信功能以及

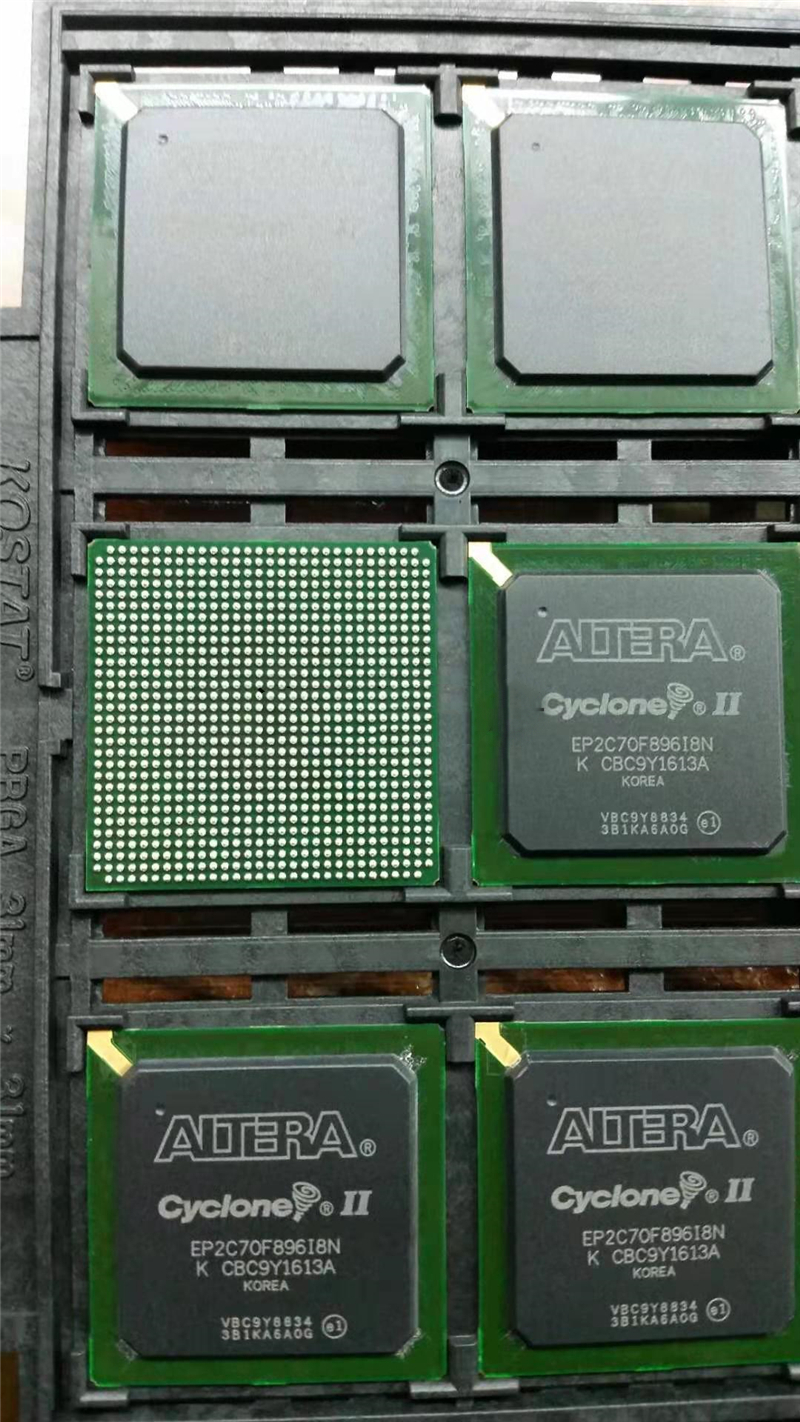

制造商: Intel

產品種類: FPGA - 現場可編程門陣列

發貨限制: Mouser 目前在您所在地區不銷售該產品。

RoHS: 詳細信息

產品: Cyclone II

邏輯元件數量: 68416 LE

自適應邏輯模塊 - ALM: -

嵌入式內存: 1152000 bit

輸入/輸出端數量: 622 I/O

工作電源電壓: 1.15 V to 1.25 V

最小工作溫度: - 40 C

最大工作溫度: + 85 C

安裝風格: SMD/SMT

封裝 / 箱體: FBGA-896

封裝: Tray

系列: Cyclone II EP2C70

商標: Intel / Altera

最大工作頻率: 260 MHz

濕度敏感性: Yes

邏輯數組塊數量——LAB: 4276 LAB

產品類型: FPGA - Field Programmable Gate Array

工廠包裝數量: 27

子類別: Programmable Logic ICs

總內存: 1152000 bit

商標名: Cyclone II

零件號別名: 973054