作者:安森美首席現場應用工程師Majid Dadafshar

CMOS 圖像傳感器的電源布局會顯著影響分辨率、幀率等性能。本文討論針對此應用設計電源方案時的重要考量。

CMOS 圖像傳感器的內部結構

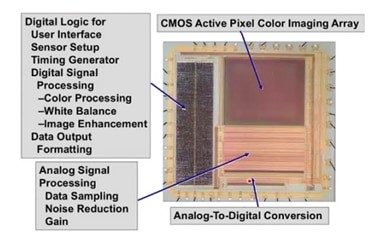

典型的 CMOS 成像系統包含有源像素顏色陣列、模擬信號處理電路、模數轉換器和用于控制接口、時序和數據讀取的數字部分。陣列的填充因數是感光部分相對于傳感器總尺寸的百分比。光電探測器是一種光敏傳感器,用于捕獲可見光子并將其轉換為電流(毫微微安級)。分辨率用于量化 CMOS 圖像傳感器中的總像素陣列數,例如,200 萬像素傳感器陣列是 1600 列和 1200 行。但是,陣列中的像素并非都是有源的(可用于光檢測),其中有些(在光學上是黑色的)像素用于黑電平和噪聲校正。

圖 1:典型的 CMOS 圖像傳感器模塊

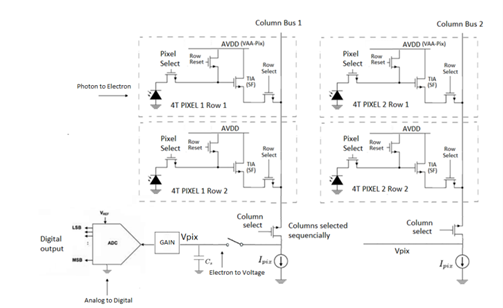

現有多種不同的像素晶體管設計,包括三晶體管 (3T)、四晶體管 (4T) 和五晶體管 (5T) 版本。在 4T 布局中,光電二極管將接收到的可見光子轉換為電荷。每個電壓一次讀取一行并放入柱狀電容器 (C) 中。然后使用解碼器和多路復用器進行讀取。

圖 2:四晶體管像素設計

幀率用于量化圖像處理陣列捕捉完整圖像的速度,一般為 30-120 fps。幀率受快門速度影響,后者控制圖像傳感器收集光線的時間。可編程時間間隔,也稱為“暗期”,在讀取最后一行之后執行其他任務時,此間隔也會影響幀率,約為讀取速率的 75%。幀是按順序逐行讀取的;最后,緩沖器將整個幀存儲為完整圖像。

電源設計考量

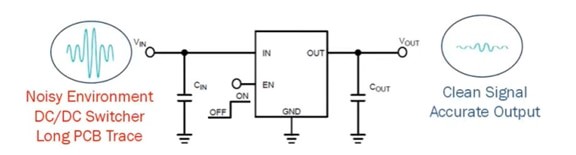

CMOS 圖像傳感器一般使用三個不同的供電軌,分別是模擬供電軌 (2.8 V AVDD)、接口供電軌(1.8 或 2.8 V DOVDD)和數字供電軌(1.2 或 1.8 V DVDD)。低壓降 (LDO)穩壓器的輸入引腳上有一個大旁路電容,可以穩定電源,幫助減少電壓波動,從而改善圖像傳感器的噪聲性能。電源抑制比 (PSRR) 衡量 LDO 抑制電源紋波引起的輸入電壓變化,或者阻斷由其他開關穩壓器導致的噪聲的能力。具有低 PSRR 的 LDO 可能導致捕獲的圖像中出現不必要的水平紋波。在針對此應用設計具有足夠高 PSRR 的 LDO 之前,可計算給定幀率所需的傳感器行頻。

圖 3:正在進行穩壓的 LDO

LDO 內部的反饋環路基本決定了工作頻率低于 100 kHz 的系統的 PSRR。對于更高頻率(高于 100 kHz)應用,仍取決于無源組件和PCB布局。因此,謹慎的 PCB 設計可以實現緊湊的電流環路,并降低寄生電感。普通 LDO 在高頻率下 PSRR 較低。雖然這對標準攝像頭來說不是問題,但更高分辨率 (50−200 MP) 和高幀率的圖像傳感器要求 LDO 在更低頻率(最高 10 kHz)下的 PSRR 高于 90 dB,在更高頻率 (1−3 MHz) 下高于 45 dB。

設計技巧

幀率 (30−120 fps) 和行速率 (22−44 kHz) 會產生動態負載,在模擬供電軌上引起下沖和過沖。在每次幀或行轉換時,獲取的電流類似于階躍負載,意味著在每次讀取幀和行(或之間)時,LDO 必須能夠處理數百毫安級的負載變化。大容量電容(在行和幀頻率下具有低阻抗)可以幫助攝像頭去耦,以減少這種負載切換引起的紋波。

圖像傳感器的每個像素都有電荷飽和水平(或最大阱容),這是在達到飽和之前像素能留存的電荷量(以電子為單位)。圖像傳感器的動態范圍(以 dB 表示)是能同時捕獲的圖像最亮和最暗部分的比率。LDO 輸出端的低頻譜噪聲密度(在 10 Hz 至 1 Mhz 之間)也有助于減少傳輸至 CMOS 圖像傳感器的噪聲量,使像素實現更大的動態范圍。最后,總體紋波和噪聲應至少低于傳感器的噪聲閾值 40 dB,在數據手冊中通常表示為信噪比 (SNR)。