XILINX公司擁有多種不同系列的FPGA芯片,隨著微電子技術的發展,芯片的結構與功能也發生了相應的變化。本文參考了XILINX系列芯片的相關資料,結合微電子電路相關知識,重點針對Virtex系列芯片,從其基本結構、CLB (可配置邏輯塊) 、IOB (輸入輸出模塊) 、可編程內連等方面進行了詳細的分析研究。最后通過比較的方式給出了各系列芯片間芯片結構以及性能上的差異。

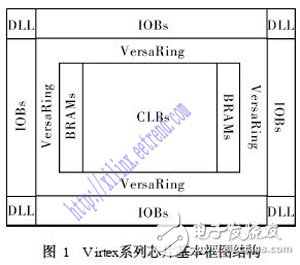

1 Virtex系列芯片基本概況Virtex系列芯片的基本電路框圖結構如圖1 所示。它主要由可配置邏輯塊( Configurable Logic Blocks, CLB)組成的規則陣列構成內部核心部分;周圍是輸入輸出模塊( Input/Output B locks, IOB) ;在管芯的四個角上有4個時鐘鎖相環;遍及整個芯片分布著4個通用低擺率的全局時鐘分配網絡;在CLB與IOB之間,有兩列RAM塊,分別位于左右對稱的兩側,這一系列的芯片可以把配置數據存在其內部的靜態存儲單元中,通過這種方式可以實現無限循環次數的重復編程,存儲在靜態存儲單元中的值控制著可配置存儲單元及內連資源,這些值在上電時加載到靜態存儲單元中,如果需要改變系統功能時可重新對其進行配置,同時,它還提供了基于函數發生器的單端口與雙端口的分布式RAM。

Virtex系列芯片最多可容納的邏輯門數為1000000門,系統時鐘頻率可達200MHz;它采用5層金屬板的CMOS工藝。

1)輸入輸出邏輯塊( IOB)

它提供了包裝引腳與內部邏輯之間的接口界面。

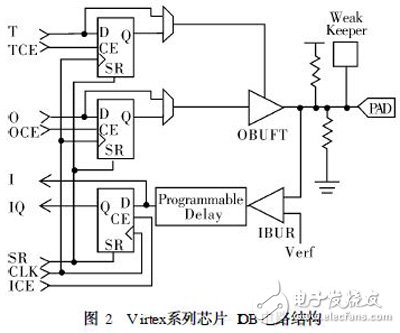

Virtex系列芯片的IOB的電路結構如圖2所示。

圖2中,三個IO寄存器既可作為D型觸發器也作為邊沿敏感的瑣存器,它們共用同一個時鐘,共用同一個置位/復位信號,但各自有獨立的時鐘以始能信號。對每一個寄存器,輸入數據可配置成同步置位、同步復位、異步預置位、異步清零,具體配置可以通過軟件編程進行控制。上拉電阻、下拉電阻以及弱保持電路是焊盤的附屬器件。配置前,與配置無關的輸出均被置于高阻狀態,下拉電阻與弱保持電路處于非活動狀態,但輸入處于激活狀態,配置模式中的全局原則控制著上拉電阻的激活,如果上拉電阻沒有被激活,所有引腳處于浮動狀態。當靜電和電壓過高時所有焊盤均可處于保護狀態之下。

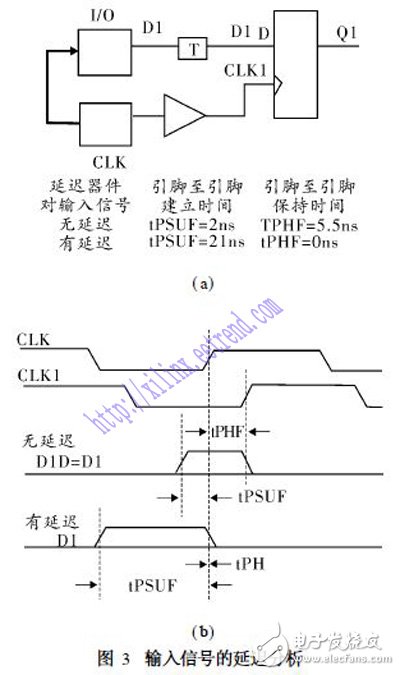

a. 輸入通路。通過可編程的輸入緩沖把信號直接或經過寄存器的輸出送入,信號在送入寄存器前,由可編程延遲器件對輸入信號進行延時配置[ 2 ] ,使信號的延時與FPGA里時鐘的分配延時相同,故輸入信號焊盤與輸入時鐘焊盤之間的保持時間為0;如果延遲器件不對輸入信號進行延時處理,則輸入信號與芯片輸入時鐘之間的保持時間不為0。如圖3所示。

圖3 ( a)中,電路圖中左邊的紅色箭頭表示從CLK焊盤到IO焊盤之間的延遲。T單元實現圖3 ( b)所示延時功能,它可以決定是否對輸入信號D1進行延時。若有延時,焊盤與焊盤之間的保持時間為0,但此時的建立時間增加到21ns;若無延時,保持時間為5. 5ns,建立時間為2ns。所以,當延時編程器件對輸入信號進行的延時是以延長建立時間作為代價的,而且代價還比較大,相當于無延遲的10倍! 圖3 ( b)是相應的對輸入信號是否進行延遲時的時序圖。另外,輸入信號對于CLK1 的保持時間是0,建立時間圖中未畫出;CLK1對于CLK也有一個延遲,這是時鐘信號通過時鐘緩沖以及全局時鐘分配網絡在整個芯片上對時鐘進行分配過程中產生的延遲。

b. 輸出通路:圖2中,輸出信號可以經過輸出緩沖直接輸出,也可先進入寄存器然后再進行輸出。每一個輸出焊盤上有一個弱保持電路,它監視著焊盤上電壓的微妙變化,并對之進行調整以匹配輸入信號。

2)可配置邏輯塊(CLB)

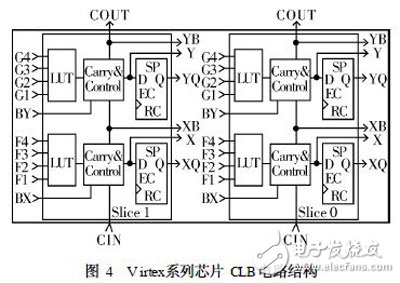

Virtex系列的CLB電路結構如圖4所示。

CLB的基本組成單元為LC (邏輯單元) 。圖中列出了兩個LC,每個LC包括兩個4輸入的函數發生器、兩個進位邏輯和兩個存儲單元。

a. LUT與函數發生器。函數發生器被用來實現一個4輸入的查找表,每個查找表可提供一個16 ×1bit的同步RAM,或形成一個可以存儲隨機的突發的快速數據的16bit的移位寄存器;同一個LC中的兩個部分可組合成一個16 ×2 - bit或32 × 1 - bit的同步RAM,或者組成一個16 x 1 - bit的雙端口的同步RAM。

b. 存儲單元。它可以被配置成D邊沿觸發器或者電平敏感的瑣存器,輸入可以是LUT的輸出也可是直接來自于LC的輸入信號,旁路掉函數發生器。

c. 快速進位邏輯。為高速算術函數的運算提供了快速運算進位功能,它支持兩個獨立的進位鏈。

3) RAM塊

Virtex系列中包含64個CLB的芯片中每列有16個RAM塊,所以共有32個RAM塊。每一個RAM塊都是完全同步的雙端口的4096 - bit的。每個端口都有獨立的配置信號,且每個端口的數據寬度都是各自獨立配置的。

4)可編程的布線陣列

包括以下幾種布線。

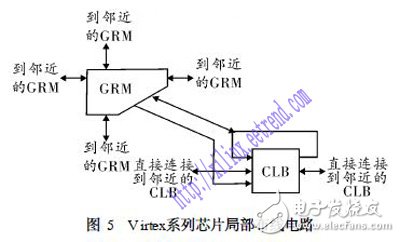

a. 局部布線: Virtex系列的局部布線有三種方式的連接,即: LUT、觸發器、常規布線矩陣(GRM)之間的連接; CLB內部把同一個CLB的輸出反饋回來作為自身LUT輸入的連接,這種連接提供了最小的延時;在相鄰的CLB間提供水平連接,這種連接消除了信號在GRM中的延遲。這三種方式如圖5所示。

b. 常規布線: Virtex系列中在CLB的通道中,水平與豎直方向各有24根單長線連入GRM中,通過GRM中的可編程開關實現是否互連,以實現CLB 間的互連;四個方向各有12條帶緩沖的16進制線每跨過6個CLB從一個GRM匯入下一下GRM;每個CLB分別在水平與豎直方向相鄰著12根帶緩沖的雙向的長線,長線的長度與CLB區域的長或寬相同。

c. IO布線:這是一種在芯片的周圍附加的布線資源,它提供了CLB 陣列與IOB 的交換界面,稱為多功能環,同時,除了能把IOB與CLB連接起來之外,還可以實現引腿之間信號的交換。

d. 直接連線:一些信號需要專門的連線來達到最優性能的實現,直接連線便實現了這一目的,在Virtex芯片中,有兩類這樣的信號:在兩個獨立網絡中,每個CLB傳輸進位信號給相鄰的CLB;水平布線資源在一個通道內提供4條三態總線來與CLB交換信號。

e. 全局布線:它為時鐘及其實遍及整個芯片的多扇出信號提供分配通路。Virtex包括兩類全局布線資源:主全局布線與次全局布線。主全局布線由4個以最小擺率來分配高扇出時鐘信號的有專門輸入引腳的全局網絡構成。次全局布線包括24 條主干線, 12 條穿過芯片上端, 12條通過芯片下端,通過這些線,每一個CLB列中可以有12條信號分布式地通過這列中的12條長線。

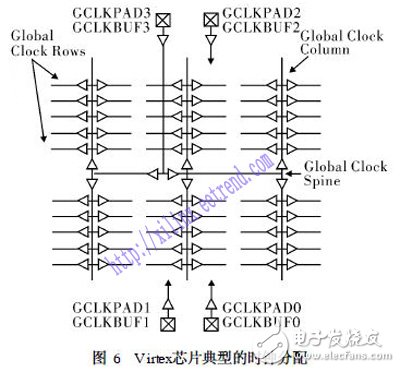

5)時鐘分配

通過主全局布線Virtex在整個芯片上提供高速、低擺率的時鐘分配。典型的時鐘分配如圖6所示。它提供了4個全局時鐘緩沖器, 4個專門的時鐘焊盤分別與每一個全局時鐘緩沖器相匹配,全局緩沖的輸入可以來自于這些焊盤,也可以來自于常規布線。

時鐘延遲瑣定環。與每一個全局時鐘緩沖器相關聯的是全數字的延遲瑣定環,它可以有效地消除時鐘輸入焊盤與遍及整個芯片的時鐘輸入之間的擺率。每個DLL可驅動兩個全局的時鐘網絡,DLL監視著總時鐘信號與被分配開的時鐘信號,自動調整時鐘延遲因素,它可以精確地實現從時鐘從焊盤輸入至其邊沿到達內部觸發器時延遲1 - 4個時鐘周期的功能。這個閉合的環通過確保時鐘邊沿同步到達內部觸發器來有效地消除時鐘分配延遲。為了保證系統時鐘在配置完畢剛開始啟動FPGA時能夠正常工作,DLL 可以延遲配置的完成直到它已經瑣定了時鐘為止。

3 結束語本文僅給出了Virtex系列芯片的內部基本結構與性能分析。現結合本文分析,對XILINX其它各系列芯片結構與性能進行如下比較。

器件容量與系統速度的提高。在芯片所容納的晶體管的門數上由較早XC3000 系列的最高7500 門的容量到Spartan - II系列的200000門直至Virtex系列的1000000門容量;在系統的時鐘速度上由原來的不足百兆到最后的200多兆,實現了質的飛躍。

與CLB相關的內置器件功能的增多。XC4000在XC3000的基礎上,增加了快速進位邏輯,從而提高了器件進行多種邏輯運算的能力與速度。

IOB方面。XC4000的IOB 中除了對輸出配置較3000更加靈活外,還增加了一個輸出的MUX,它可以在輸出通路中實現多種基本的函數運算;而在Spartan- II系列與Virtex系列的IOB中則更加強了對延時的控制,通過專有的延時電路可以實現信號與時鐘的良好匹配。

系統內連方面, Spartan - II系列與Virtex系列的內連,連接方式比XC4000更加條理化與模塊化,隨著器件內部時鐘的大量使用,這兩系列把時鐘的分配單獨劃分出一系統,建立了單一的時鐘分配網絡。

·XC6SLX45-2FGG484C

·XC6SLX45-L1CSG324I

·XC6SLX45T-2FGG484I

·XC6SLX75T-3FGG484I

·XC6SLX9-2CSG324C

·XC6SLX9-2CSG324I

·XC6SLX9-2FTG256C

·XC6SLX9-2FTG256I

·XC6SLX9-2TQG144C

·XC7A100T-2FGG484I

·XC7A75T-2FGG676I

·XC7K160T-2FFG676C

·XC7K160T-2FFG676I