為將設計團隊的生產力提升到全新的水平,以及向更廣泛的軟件工程師用戶推廣其全可編程 FPGA、SoC和3D IC,賽靈思近期新增了兩款SDx™開發環境系列成員。新推出的SDAccel™開發環境使沒有任何FPGA經驗的數據中心設備編程員都能夠運用OpenCL™、C或C++語言針對數據中心和云計算基礎設施對賽靈思FPGA進行編程,設計出的FPGA設備性能功耗比遠超基于GPU和CPU的設備。賽靈思還推出了SDSoC™開發環境,支持同樣沒有FPGA經驗的軟件開發人員運用C或C++語言針對賽靈思及第三方平臺開發商推出的Zynq®-7000全可編程SoC和UltraScale+™ MPSoC平臺創建各種系統。

SDx環境是賽靈思全可編程抽象化計劃的最新產品。該計劃旨在幫助軟件工程師和系統架構師方便地編程賽靈思器件,同時開發環境可根據他們的需求量身定制。

賽靈思公司企業戰略與市場營銷部高級副總裁Steve Glaser指出:“SDNet、SDAccel與SDSoC這一完美組合將為系統和軟件工程師提供熟悉的類似CPU、GPU和ASSP的編程環境,這些工程師將首次盡享全可編程器件帶來的獨特優勢,諸如定制加速功能,性能功耗比提升10倍乃至100倍,任意設備件間連接,以及提供下一代智能系統所需的保密性和安全性。賽靈思正力助下一代系統做到進一步互聯,實現軟件定義和虛擬化,同時還必須支持基于軟件的分析,更多云端計算功能,這通常是普遍視頻和嵌入式視覺技術所需要的。這就要求SDx軟件定義編程環境和異構多處理技術采用新型UltraScale FPGA和MPSoC。”

2014年春季SDNet™開發環境(詳見《賽靈思中國通訊第87期》)推出后不久就推出了SDAccel和SDSoC這兩款新的開發環境。

SDx新環境能幫助軟件工程師和系統架構師對賽靈思器件的FPGA部分進行編程,這些環境也能幫助擁有硬件工程設計資源的設計團隊提升生產力,快速集成到優化系統上,進而加速產品上市進程。有了可行的系統設計,硬件工程師能集中精力優化FPGA布局和性能,實現更高的系統效率,同時軟件工程師則能進一步優化應用代碼。

全可編程抽象化

賽靈思于2008年在新任CEO Moshe Gavrielov領導下開始規劃7系列全可編程系列FPGA、3D IC和Zynq-7000 全可編程 SoC時,就明顯發現7系列和未來產品線的所有產品均具有豐富的功能,完全能讓客戶將賽靈思器件作為最新最具創新性產品的核心。

這些全可編程器件比賽靈思早些年的膠合邏輯FPGA高級得多,實現了任何其他架構所無法企及的系統功能和最終產品差異化。為了最大化這些最新器件的價值,在競爭中脫穎而出,管理層認識到賽靈思必須開發出相關工具和方法,幫助系統架構師乃至嵌入式軟件開發員(而僅僅只有FPGA專家),去進行賽靈思最新器件的編程工作。此外,公司還必須針對高增長市場,為軟件工程師開發出設計環境,并根據設計人員習慣使用的工具和流程來定制這些環境。此外,加強與MathWorks和國家儀器(Nl)等公司聯盟也勢在必行,這些公司已經構建了各種環境,使非傳統FPGA用戶能夠充分利用賽靈思全可編程器件的功率效率和靈活性優勢。

對老客戶來說,如果能為設計團隊的每個成員都提供相應的設計環境,那就能確保高效性,縮短產品上市時間。如果這些環境足夠高級,就能真正推廣全可編程FPGA和Zynq SoC設計,讓那些沒有FPGA設計經驗的架構師和軟件工程師無需硬件設計人員幫助就能進行器件編程。全球軟件工程師人數與硬件工程師人數比為10:1。因此,提供這種開發環境(或支持這種開發環境的硬件平臺)的賽靈思及其聯盟計劃合作伙伴既能擴大用戶群,又能增加營收。

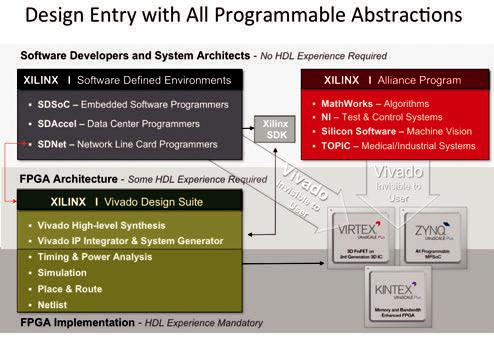

該戰略和支持軟件工程師及系統架構師利用根據其設計需求量身定做的環境進行賽靈思器件編程的后續開發工作就是賽靈思所謂的全可編程抽象化(如圖1所示)。

圖1 – 利用新的SDx設計環境和聯盟成員提供的環境,賽靈思正幫助更多創新者充分發揮賽靈思全可編程器件的作用,為下一代產品帶來更大增值。

VIVADO HLS和IPI:設計抽象的第一步

2011年,設計抽象邁出了重大的第一步,那就是賽靈思收購了私企AutoESL廠商的高層次綜合(HLS)工具。繼并購之后,賽靈思于2012年公開發布了集成到ISE®設計套件和Vivado®設計套件工具流程中的HLS技術。根據Berkeley Design Automation的詳細調研(結果表明AutoESL的HLS工具最簡便易用,而且是EDA產業所有HLS工具中能提供最佳結果質量的HLS),賽靈思選擇了AutoESL技術。HLS源于EDA世界,這也意味著工具使用模型面向的是ASSP和片上系統(SoC)架構師以及擁有C和C++編程經驗、同時對硬件描述語言(Verilog和VHDL)及芯片設計需求有一定工作了解的成熟設計團隊。

利用Vivado HLS,具有豐富技能的架構師和設計團隊能用C和C++創建算法,同時利用Vivado HLS來編譯并轉換那些算法為RTL IP模塊。隨后,FPGA設計人員能將這個模塊及其它模塊集成到創建或授權的RTL中,并用賽靈思的IP Integrator(IPI)工具將IP匯編到設計中。隨后,FPGA設計人員能將匯編設計一步步通過Vivado流程,執行HDL仿真、時序與功耗優化、布局布線等。最終,設計人員生成網表/比特文件并配置目標全可編程器件的硬件。如果設計包含處理器(Zynq SoC或MPU軟核),配置后的器件隨即可供嵌入式軟件工程師編程。

為了幫助嵌入式軟件工程師應對繁雜的編程工作,賽靈思提供了基于Eclipse的集成設計環境,即賽靈思軟件開發套件(SDK),其包含編輯器、編譯器、調試器、驅動程序和面向Zynq SoC或FPGA的庫,其內嵌了賽靈思的32位MicroBlaze™軟核。該SDK于10多年前推出,隨著賽靈思器件上處理器集成的發展變化而得到了大幅改進,此前器件上集成硬化的DSP Slice和軟核MCU和MPU(8位、16位和32位),到Virtex®-4和Virtex®-5 FPGA時已轉變為集成硬化的32位PowerPC®;到Zynq SoC已轉化為集成32位ARM®處理器;而到即將推出的Zynq UltraScale+ MPSoC則發展到集成64位ARM處理器。

聯盟成員為更多用戶帶來增值

10多年來,賽靈思與國家儀器(NI)和The Math-Works公司一直保持密切合作。這兩家公司致力于為其服務的特定用戶提供量身定制的獨特高級開發環境。

國家儀器(NI)(德克薩斯州奧斯汀)提供的硬件平臺深受控制和測試系統創新者歡迎。賽靈思的FPGA和Zynq SoC為NI RIO平臺提供動力。國家儀器(NI)的LabVIEW開發環境是用戶友好型圖形化程序,底層運行Vivado設計套件,因此國家儀器(NI)的客戶無須了解任何FPGA設計細節。一些人或許根本不知道RIO產品的核心其實是賽靈思器件。他們只需在LabVIEW環境中對其系統編程即可,NI硬件能提升其開發的設計性能。

就MathWorks(馬薩諸塞州納蒂克)而言,該公司10多年前為其MATLAB®、Simulink®、HDL Coder和Embedded Coder添加了FPGA支持,底層運行賽靈思的ISE和Vivado工具,而且完全自動化。因此,公司的用戶——主要是數學算法開發人員——能開發算法并大幅提升算法性能,而且能在FPGA結構上簡便運行算法。

10年前,賽靈思為其ISE開發環境添加了FPGA架構級工具——系統生成器(System Generator),近期又給Vivado設計套件添加了,以幫助具備FPGA知識的團隊進一步調節設計,實現算法性能增益。MathWorks和賽靈思兩家公司技術的強強組合,有助于客戶公司推出成千上萬種創新產品。

近期,其他公司也開始為賽靈思環境做出貢獻。賽靈思近期歡迎TOPIC Embedded Systems和Silicon Software這兩家歐洲公司加入其聯盟計劃,特別是歡迎其針對醫學和工業市場的高級開發環境。

TOPIC Embedded Systems(荷蘭埃因霍溫)擁有獨特的開發環境DYP-LO,《賽靈思中國通訊第89期》對其進行了詳細介紹。該環境面向Zynq SoC,很快也將面向Zynq MPSoC,對系統級設計采用統一方法,從而使系統架構師能夠用C或C++創建系統設計結果,并在Zynq SoC的雙核ARM Cortex™-A9處理系統上運行該結果。一旦用戶發現設計某些部分在軟件中運行太慢,可以將這些部分拖放到窗口中,將C語言轉化為FPGA邏輯(底層運行Vivado HLS),并將其放入Zynq SoC的可編程邏輯中。來回交換代碼片段,直到達到最佳系統性能。TOPIC最初用于醫療設備開發,目前也開始與工業設備制造商合作。

Silicon Software(德國曼海姆)是支持軟件工程師利用賽靈思全可編程器件的最新聯盟成員。公司的VisualApplets圖形圖像處理設計環境可幫助面向Zynq SoC平臺的系統架構師和軟件工程師打造工業機器視覺應用創新,而且無需硬件工程師的協助。在2013年SPS Drives行業展會的賽靈思展臺上,Silicon Software展示了其用VisualApplets環境開發的光學檢查系統。演示顯示通過采用VisualApplets環境將圖形處理任務從Zynq SoC的處理系統轉交給器件的FPGA邏輯來執行,能將系統性能提升10倍。

借助SDx推廣FPGA和SOC設計

借助SDx軟件定義開發環境,賽靈思將面向關鍵市場的軟件開發人員和系統架構師構建一系列比較高級的設計入門環境。SDAccel和SDSoC在底層自動運行整個Vivado流程,無需直接使用Vivado工具,也無需硬件工程師的協助。SDNet不會訪問Vivado HLS,針對線路卡架構師,其提供了獨特的兩步使用模型。

在第一步中,線路卡架構師采用直觀的類似C語言的高級語言而不是晦澀的微代碼來設計需求,并制定網絡線路卡規格描述。SDNet開發環境根據規格描述生成RTL版設計。流程隨后需要硬件工程師在目標FPGA中實現RTL。

在第二步中,SDNet還允許網絡公司用高級語言測試和更新協議,并升級線路卡的功能,即便在現場部署后也能做到,而且無需硬件設計參與。這個流程有助于企業快速創建并更新線路卡,這種靈活性對軟件定義網絡而言非常重要。

SDAccel和SDSoc這兩個新環境將SDx理念推廣到新的應用領域。

SDACCEL可優化數據中心性能功耗比

《數據中心學刊》(Data Center Journal)2014年3月的一篇文章指出,谷歌、Facebook、亞馬遜、領英等公司核心部分——數據庫——“消耗的電力占全球電力3%以上,同時產生2億公噸CO2”。如此巨大的能耗,數據中心一年電費超過600億美元。即便對最大規模網絡公司來說,功耗也會嚴重削減盈利性,而且對環境也會產生不可估量的影響。

隨著越來越多的企業期望采用云計算和大數據分析技術;視頻和流媒體的全球性普及,以及越來越多的人加入無線網并升級到未來5G網絡,對數量更多、性能更好的數據中心的需求呈幾何級無止境增長趨勢。《數據中心學刊》文章指出,從當前趨勢看,到2017年數據中心流量預計將達7.7ZB,這意味著數據中心的功耗如果不能得到有效控制將會出現大幅增長。當今大多數數據中心的功耗主要源于其基礎組件——Intel x86處理器。目前MPU能提供良好但不是最佳的性能,而且功耗很高。

目前全球龐大的的軟件工程師隊伍均發現MPU是最容易編程的器件。要解決數據中心性能問題,許多公司一直在設法構建采用圖形處理單元(GPU)或通過GPU實現CPU系統加速的設備。GPU的性能大大超越數據中心的CPU,但不幸的是功耗要高很多。性能雖然很高,但功耗巨大。

為集兩者之大成,許多企業均轉而采用以FPGA為中心的方法,將FPGA與其它處理器結合使用,以實現數據中心設備性能最大化。

許多數據中心設備廠商已證實,分立式FPGA結合分立式CPU使用,雖然每個卡的功耗會增加一點點,但性能卻得到大幅提升,從而可大幅提升性能功耗比。還有人認為,通過采用一顆在單個SoC上集成x86處理器內核和FPGA邏輯的芯片,有望進一步提升性能功耗比。還有人認為,在單個SoC上集成FPGA邏輯和64位ARM處理器IP似乎能帶來更低功耗但同樣高性能的解決方案。

在數據中心使用FPGA的主要障礙就是編程問題。數據中心開發人員習慣于x86架構編程,這些開發人員通常只有純軟件編程背景。幫助開發人員將CPU程序轉向更快的GPU的第一步就是業界OpenCL語言的開放開發。過去2年來,OpenCL取得進一步發展,使客戶能夠針對FPGA進行編程,從而為未來數據中心設備架構乃至無所不在網絡創造了新的機遇。

通過推出SDAccel環境,賽靈思彌補了編程鴻溝,并為數據中心工程師使用OpenCL、C或C++編程FPGA平臺鋪平了道路,而且無需硬件工程師介入。賽靈思公司設計方法市場高級總監Tom Feist表示,針對OpenCL、C和C++的SDAccel開發環境使數據中心編程人員能夠打造出比CPU和GPU系統性能功耗比高出25倍的設備。

Feist指出,在SDAccel流程中(見圖2,SDAccel開發環境演示),x86 CPU結合運行賽靈思20nm Kintex® UltraScale FPGA的加速卡,軟件開發人員能發現需要加速的應用,并用OpenCL編碼和優化內核,再為CPU編譯和執行應用。隨后他們再來評估并調試內核,直到找到周期精確的模型。接下來,再用SDAccel編譯代碼,并自動實現在FPGA中(可能因為Vivado在底層運行)。隨后就能運行應用,驗證通過卡加速后的應用性能以及與單純用CPU運行的性能對比。Feist指出:“他們能循環運行迭代,直到找到性能和功耗之間的最佳平衡,相對于CPU和GPU實現方案,性能功耗比可提升多達25倍。”

圖2 – 在本SDAccel開發環境演示中,工程師 Henry Styles介紹了如何通過使用內含Alpha Data ADM-PCIE-7V3加速器的標準64位x86工作站來運用SDAccel開發環境實現加速。

在本期《賽靈思中國通訊》中,Feist和他的同事詳細介紹了SDAccel環境,后續文章則介紹SDAccel的工作原理(見第38頁和42頁) 。

SDSOC讓嵌入式系統創新者輩出

SDNet讓線路卡開發人員利用獨特的軟定義方式能夠快速創建下一代網絡,而SDAccel則能讓數據中心設備廠商實現下一代數據中心的最佳性能功耗比。新的SDSoC開發環境或許能為賽靈思用戶群帶來最廣泛的影響。這是因為SDSoC針對廣泛的嵌入式系統設計團隊,特別是軟件工程師,這些軟件工程師設計面向的是賽靈思Zynq SoC所服務的大部分市場。SDSoC環境現在能幫助用戶配置邏輯——不光是對運行Zynq SoC硬件平臺的嵌入式系統處理器編程——而且能使用C和C++語言。

SDSoC產品經理Nick Ni指出:“軟件開發人員習慣于對主板、ASSP平臺和ASIC進行編程,且無需硬件工程師參與。有了SDSoC開發環境,他們就用類似ASSP的方式對Zynq SoC和MPSoC平臺進行編程。SDSoC的獨特之處在于現在我們能在Eclipse IDE環境中用C或C++語言面向Zynq SoC和Zynq UltraScale+ MPSoC平臺創建完整的系統設計。

Ni表示,使用SDSoC環境,嵌入式軟件開發人員能運用C或C++語言創建設計并進行測試,以發現Zynq SoC處理系統上哪些部分運行得不佳。一旦發現可疑代碼,便突出顯示并命令SDSoC環境自動將該代碼分區到Zynq SoC的可編程邏輯中,以加速系統性能。Ni指出,SDSoC環境只需點擊按鈕就能把軟件功能移到FPGA邏輯中,無需硬件工程師介入。SDSoC中的編譯器將生成整個Vivado項目,并為目標硬件平臺生成可引導的軟件映像。

Ni指出:“利用針對我們Zynq SoC的SDSoC環境,我們主要是讓我們的嵌入式軟件工程師變成系統工程師。” (見圖3,SDSoC開發環境演示)

圖3 – 在本SDSoC開發環境演示中,首席工程師Jim Hwang用SDSoC構建簡單的圖形處理流水線,以檢測運動,并在以60fps速率運行的實時HD 1080p視頻流中插入運動邊緣。

SDSoC環境利用帶有用戶指定的C/C++代碼的宏編譯器,可在Zynq SoC邏輯中實現加速。通過在底層運行Vivado設計套件,該環境可自動將該代碼返回IP模塊并將該模塊配置為器件的邏輯,從而自動生成軟件驅動程序。

SDSoC可為基于Zynq全可編程SoC的開發板(包括ZC702和ZC706),以及第三方和特定市場平臺(諸如ZedBoard、 MicroZed、ZYBO以及視頻與圖像開發平臺)提供板支持包 (BSP)。

Ni 表示:“我們今后幾個月將為SDSoC添加更多BSP,尤其是隨著越來越多第三方平臺公司用Zynq SoC開發系統。SDSoC有助于賽靈思以及采用Zynq SoC開發平臺的公司擴大用戶群。”

Ni同時指出,SDSoC環境的主要目的是讓大量嵌入式軟件設計人員能用賽靈思Zynq SoC創建完整的系統,不過有傳統FPGA背景的用戶和設計團隊也能從該環境受益匪淺。

Ni指出:“它能幫助設計團隊快速用C和C++語言設計系統架構,然后嘗試不同的配置,以獲得所需的最佳性能。如果他們團隊里確實有FPGA設計人員,則能讓其通過Vivado工具來進一步優化模塊和邏輯布局。”

XCZU19EG-L1FFVC1760I

XCZU15EG-L1FFVB1156I

XCZU11EG-L1FFVC1760I

EPM3512AQC208-7N

EPM3512AQI208-10N

EP4SE230F29I4

EP4SE230F29C4

EP4SE230F29I3

EP4SE230F29C2N

EP4SE230F29C4N

EP4SE230F29I4N

XC6VSX315T-1FF1156C