大家使用xilinx的多die FPGA時,或多或少的都遇到過時序收斂問題,那么對于多die的FPGA我們應該如何做好設計了。

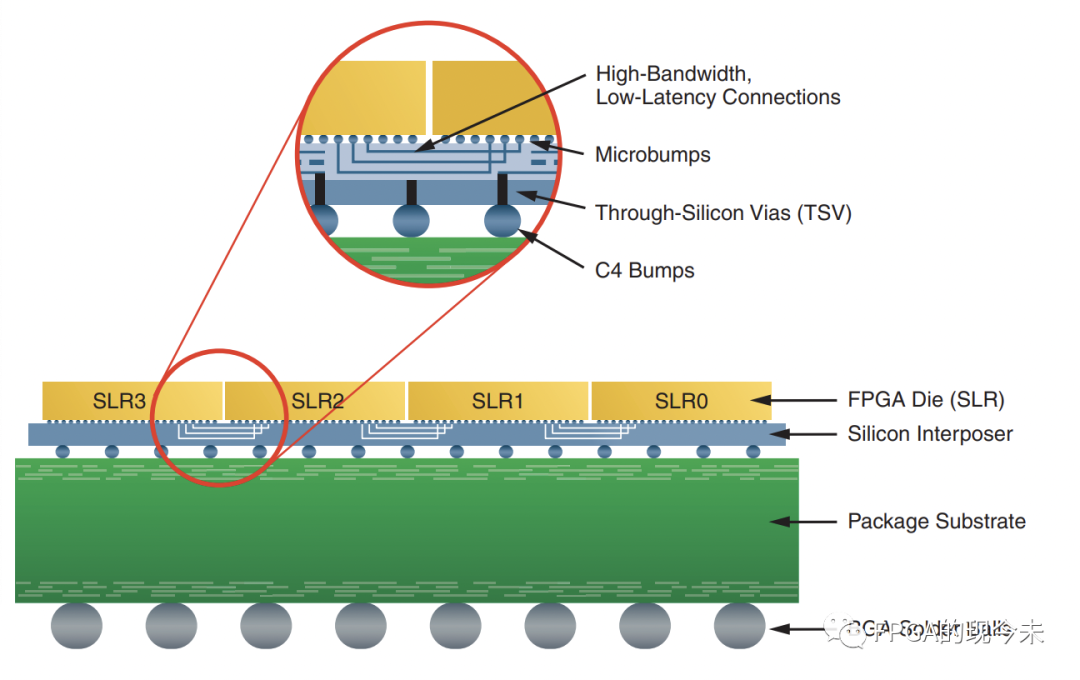

多die芯片其實是SSI(Stacked Silicon Interconnect)芯片,其結構如下圖所示。其實就是在一個封裝里,把多個芯片,也就是我們說的SLR(Super Logic Region)用interposer“綁”在一起,SLR之間的連接用專用布線資源SLL(Super Long Line)。

該截圖來自xilinx文檔872 - Large FPGA Methodology Guide (v14.3)

多die芯片為什么容易出現時序問題了,一個是SLL資源有限,兩個SLR之間的SSL資源是有限的,比如U55N卡上2die芯片的SSL有23040。第二個就是本身die之間的走線延時相對比較長。這里就作者曾經遇到的問題總結下,如何從方案的角度規劃,提前規避這類時序收斂問題。

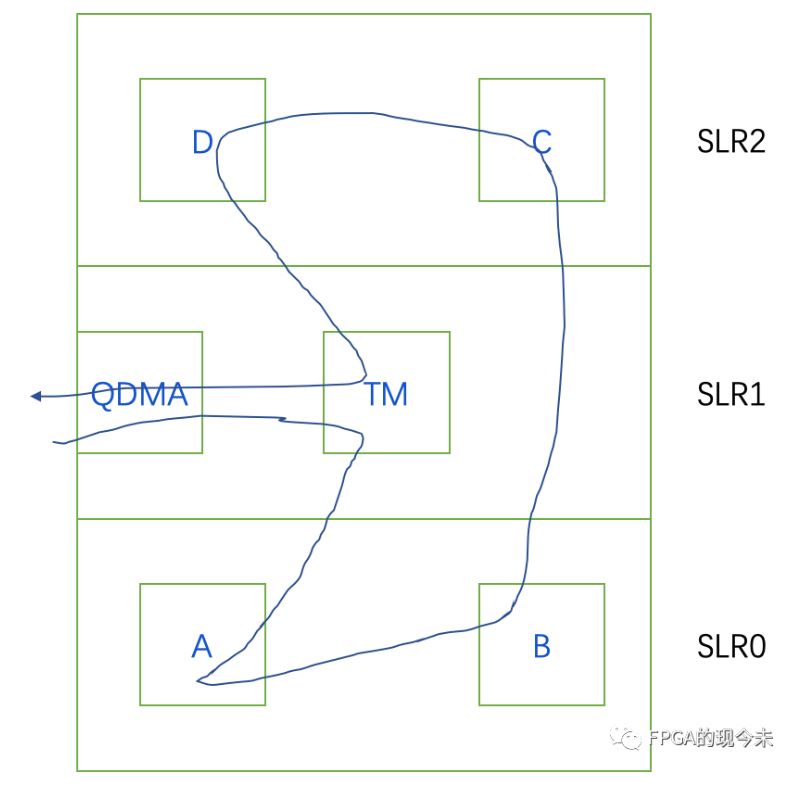

第一、從方案架構設計的角度看,FPGA的設計也就是數據流的設計,即數據流在不同模塊之間的走動。多die芯片中,關鍵就是處理數據流跨die的問題。在方案設計階段,首先要考慮一級模塊在各個die中的分布。如何分配各個一級模塊,如下圖所示,主要從2個方面考慮。

(1)、資源,各個一級模塊分布在各個die的時候,要進行合理的資源評估,考慮到資源占用情況,建議每個die中LUT不要超過70%,REG不要超過80%,RAM不超過80%。即moudle A + moudle B的資源盡量不要超過上述限制,如果超過,就要考慮把一個模塊做拆分,移入SLR1或者SLR2中。

(2)、數據流,以die為單位,做到高內聚、低耦合。一級模塊之間的接口要簡單,盡量采用流式接口。數據流也要簡單,不要在各個die之間來回穿越。即一級模塊劃分的時候,不斷要考慮資源,還要考慮數據流的走向。

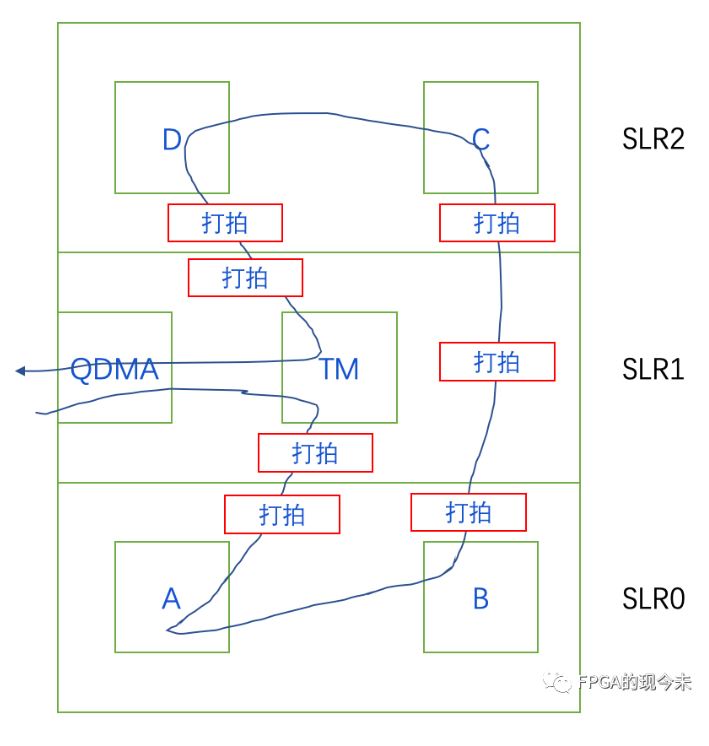

第二、在具體實現中,對于跨die的信號處理,官方的文檔(ug949)中提供了2種方式,一種是通過約束的方式使用LAGUNA寄存器,一種是通過自動流水打拍的方式。秉承問題的解決能用代碼就不用約束的思想,這里介紹一種和官方指導的第二種方案類似的方法,但是是用RTL代碼解決,可移植性更好。

如下圖所示,紅色打拍邏輯(將所有的跨die信號打2-3拍)插入在跨die數據流的兩側。對于穿越整個die的數據流,比如module B到module C的數據流,可以在中間die插入一個過橋的打拍模塊。這種方案在實踐中被證明也能很好地解決時序收斂問題。

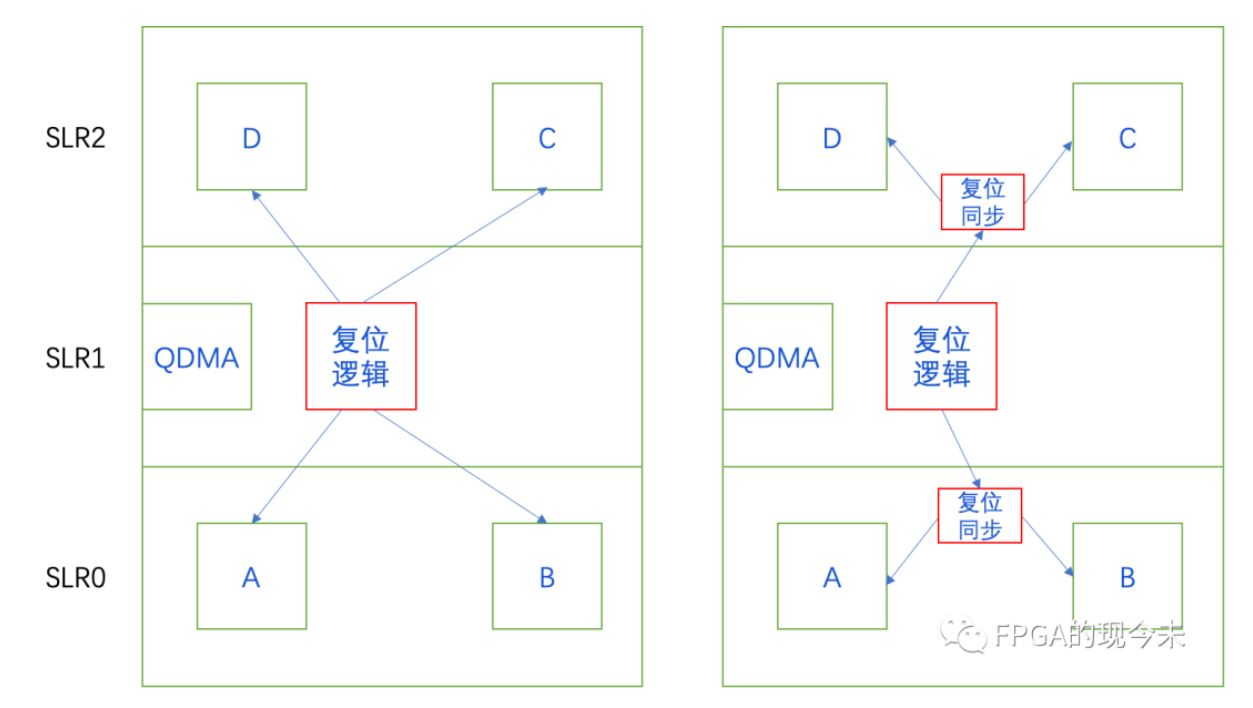

第三、復位信號的處理。跨die邏輯中有一類時序收斂問題就是復位信號的問題。筆者曾遇到一個問題,如下左圖所示,復位邏輯在中間的die,復位3個die的所有邏輯。每個die的資源消耗比較高,LUT在70%,RAM在80%,REG相對好點,不到50%。最終因為扇出較大,導致Recovery不滿足。

解決方案很簡單,就是將復位信號先同步到各個die后,只復位一個die的邏輯,這樣很好地解決了大量復位信號跨die問題,如下右圖所示。

總結,解決多die FPGA的時序收斂問題,就是合理規劃數據流、復位的方案,跨die數據流做好“橋接”。

XC6SLX75T-3FGG484I

XC6SLX9-2CSG324C

XC6SLX9-2CSG324I

XC6SLX9-2FTG256C

XC6SLX9-2FTG256I

XC6SLX9-2TQG144C

XC7A75T-2FGG676I

XC7K160T-2FFG676C

XC7K160T-2FFG676I

XC7Z010-2CLG400I

XC7Z020-1CLG400I

XC7Z030-1FBG484C

XC7Z045-2FFG900I

XCKU060-1FFVA1156C

XCKU095-1FFVA1156I

XCKU15P-2FFVA1156E

XCVU13P-2FHGB2104E