Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產品介紹

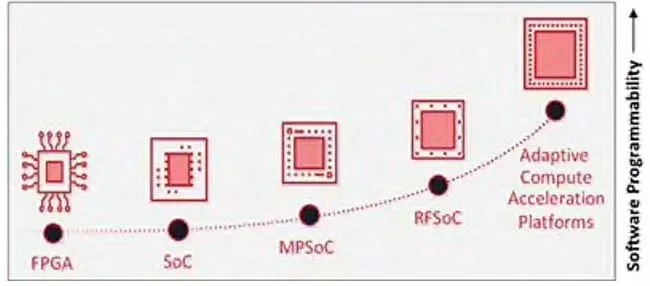

Xilinx提供各種各樣的可編程器件產品,性能和功能從中等到極高都有。范圍從傳統的FPGA到SoC(具有單個硬核心處理器的FPGA可編程結構)、MPSoC(具有多個硬核心處理器的FPGA可編程結構)、RFSoC(具有RF功能的MPSoC)和ACAP(自適應計算加速平臺)(圖1)。

圖1:隨著時間的推移,Xilinx架構產品組合已經從僅包含可編程結構的簡單FPGA,一直演變到可編程結構使用硬核心處理器增強的SoC器件、具有多個處理器的MPSoC、具有RF功能的RFSoC,再到針對AI等應用的最新一代ACAP。(圖片來源:Max Maxfield)

Xilinx擁有非常廣泛的產品組合,涉及非常多的細分市場,并提供了各種各樣的部署方法,因此對于剛接觸FPGA的新手來說,可能很難了解“全局”。

Xilinx所耕耘的市場包括但不限于數據中心(計算、網絡、存儲);通信(有線、無線);航空航天與國防;工業、科學和醫學 (ISM);測試、測量和仿真 (TME);以及汽車、廣播和消費品。

對于部署方法,這些包括Xilinx自稱的硬件自適應器件,其中包括芯片、評估板和開發套件;可部署的終端系統,包括系統級模塊 (SoM) 和PCIe加速卡;以及FPGA即服務 (FAAS),包括通過領先的云提供商(包括Amazon Web Services[AWS]、Alibaba.com和Nimbix.net)評估和利用Xilinx技術。

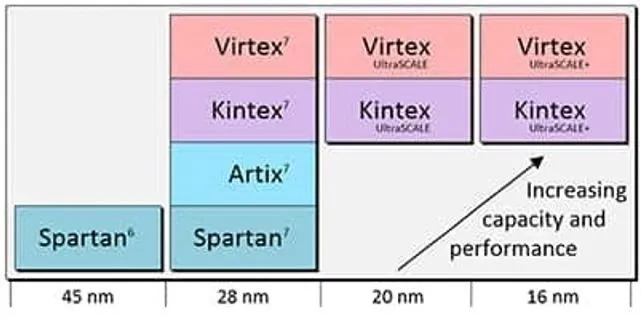

對于Xilinx的FPGA產品,一種分類方法是通過工藝技術節點(圖2)。

圖2:Xilinx的FPGA產品提供了全面的多節點產品組合,可滿足各種應用的需求。(圖片來源:Max Maxfield)

根據目標應用,設計人員可以選擇基于較早的技術節點來實現低成本、小基底面的FPGA,或者針對最新的網絡應用等,選擇基于最新技術節點來實現高容量、高帶寬、高性能器件。

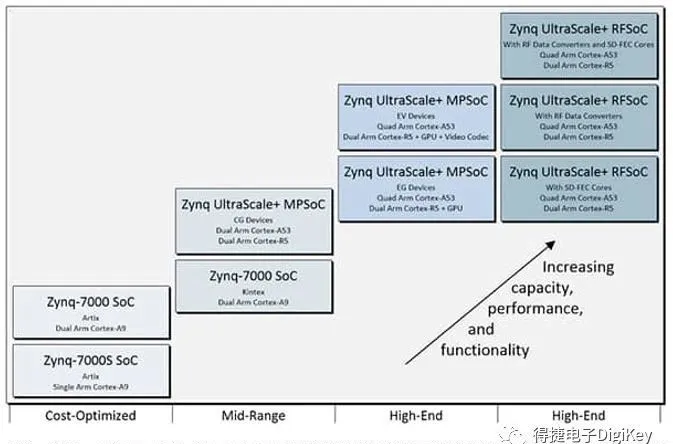

對于需要一個或多個硬處理器內核(以及GPU、編解碼器和軟判決前向糾錯 [SD-FEC] 內核等其他強化功能)的設計,Xilinx提供了一個以Zynq命名的器件產品組合。Zynq的SoC、MPSoC和RFSoC產品的摘要如圖4所示。這套解決方案為設計人員提供了廣泛的功能,能協助優化功耗、性能、成本和上市時間。

圖3:Xilinx的SoC、MPSoC和 RFSoC產品將處理器的軟件可編程性與FPGA的硬件可編程性集成在一起,為設計人員提供了系統性能、靈活性和可擴展性。(圖片來源:Max Maxfield)

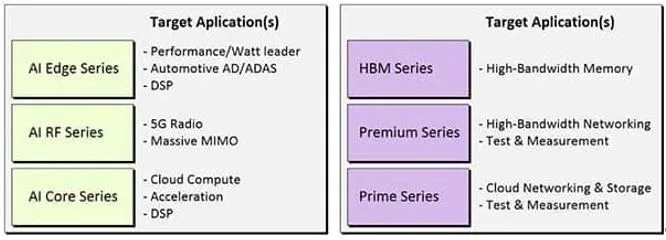

Xilinx的最新產品是Versal自適應計算加速平臺 (ACAP) 器件,所有這些器件均基于7納米 (nm) 工藝技術節點來實現。ACAP是高度集成的多核心計算平臺,可以適應不斷演進的各種算法。它們可以在硬件和軟件級別進行動態定制,以適合各種應用和工作負載。ACAP 是圍繞可編程片上網絡 (NoC) 進行構建,硬件設計人員和軟件開發人員都可以輕松對其進行編程。

Versal器件的新功能包括智能引擎,即用于ML和DSP工作負載的大規模矢量處理器陣列;可移動TB級數據的高帶寬、低延遲和低功耗可編程NoC;以及一個集成的Shell,可通過預先構建的核心基礎結構和系統連接性來提高性能、利用率和生產率。

圖4顯示了Versal ACAP產品組合的概述。

圖4:Xilinx的Versal ACAP是高度集成的多核心計算平臺,可以適應不斷演進的各種算法。ACAP可以在硬件和軟件級別進行動態定制,以適合各種應用和工作負載。(圖片來源:MaxMaxfield)

正如將在設計工具部分中的討論,有關Versal器件的一個關鍵區別是新的軟件堆棧。該堆棧主要面向數據科學家和軟件工程師,以及傳統硬件設計工程師。

市場上有各種各樣的Xilinx器件可供選擇。一些代表性的產品是Artix-7 FPGA、Kintex UltraScale FPGA、Kintex UltraScale+ FPGA、來自Trenz Electronic GmbH的Zynq-7000 SoC模塊,以及Zynq UltraScale+ MPSoC。

同樣,也有各種各樣的評估板和開發板可供選擇。一些代表性的產品包括來自Digilent的Artix-7 FPGA評估板、來自Analog Devices的Kintex UltraScale FPGA評估板、來自Xilinx的Kintex UltraScale+ FPGA評估板、來自Digilent的Zynq-7000 SoC FPGA評估板,以及來自Xilinx的Zynq UltraScale+ MPSoC FPGA評估板。

使用Xilinx的FPGA、SoC和ACAP進行設計和開發

Xilinx真正區別于競爭對手的一個因素是:設計工具和流程的廣度和深度。

在本FPGA系列文章的第1部分中,我們指出這些器件的傳統設計方法是讓工程師使用Verilog或VHDL等硬件描述語言(HDL),在抽象級別(即寄存器傳送級 [RTL])上捕獲設計意圖。首先可以對這些RTL描述進行仿真,以驗證其是否符合要求,然后將其傳送給綜合工具,生成用于對FPGA進行編程的配置文件。

抽象的下一步是捕獲設計意圖,主要是使用C/C++之類的編程語言或SystemC這樣的特殊實現工具;后者是一組C++類和宏,可提供事件驅動的仿真接口。這些方法有助于并發進程的仿真,每個進程都使用簡單的C++語法進行描述。對于此類描述,可以通過像常規程序一樣運行來進行分析和配置,然后傳遞給高級綜合 (HLS) 引擎,由該引擎輸出RTL,而RTL會傳輸至常規綜合引擎。

所有這些功能都包含在Vivado設計套件HLx版中,其輸出是配置比特流,隨后會加載到目標FPGA、SoC、MPSoC、RFSoC或ACAP器件中。除了允許硬件開發人員利用基于C語言的設計和經優化的設計復用,Vivado還提供IP子系統復用、集成自動化和加速的設計收斂功能(圖5)。

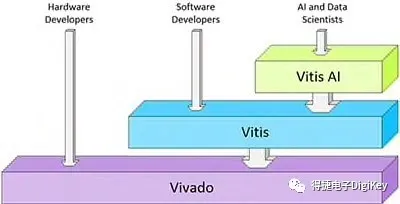

圖5:Xilinx的Vivado和Vitis設計工具堆棧的高級視圖反映了用戶如何能以最合適的抽象級別使用這些工具。硬件設計人員使用Vivado,軟件開發人員使用Vitis,而AI和數據科學家使用Vitis AI。(圖片來源:Max Maxfield)

下一個抽象級別由Vitis統一軟件平臺支持,該平臺使軟件開發人員能夠無縫構建加速型應用。從概念上講,Vitis的上面是Vitis AI,它讓AI和數據科學家可以在TensorFlow抽象級別工作。Vitis AI是在Xilinx硬件平臺上進行AI推理的開發平臺,同時包括邊緣設備和Alveo PCIe卡。該平臺由優化的IP、工具、庫、模型和示例設計組成,旨在充分利用Xilinx的FPGA和ACAP器件上的AI加速潛力。

Vitis AI饋送至Vitis,而Vitis自身饋送至Vivado。圖6中的關鍵點在于,用戶僅“看到”他們需要“看到”的內容。也就是說,硬件開發人員將僅“看到”Vivado,軟件開發人員將僅“看到”Vitis,而AI和數據科學家將僅“看到”Vitis AI。這樣,用戶就可以在最合適的抽象級別使用這些工具。

若為軟件開發人員提供Vitis之類的工具套件,將他們與底層硬件隔離開來,便可使FPGA面向更多的開發人員開放。同樣,若為AI和數據科學家提供Vitis AI之類的工具套件,使他們能夠專注于自己的抽象級別并將其與底層軟件隔離開來,則又會使FPGA面向新的開發人員群體開放。

在提供這些功能方面,Xilinx走在了全行業的前沿,致力于將FPGA工具提升到更高的設計抽象級別,這將使開發人員能夠更輕松地利用這些器件的功能,并將其集成到接下來的設計中。

總結

最佳處理設計解決方案常常是由處理器與FPGA的組合提供,或由FPGA單獨提供,或以硬處理器內核作為部分結構的FPGA提供。作為一項技術,FPGA多年來發展迅速,能夠滿足靈活性、處理速度、功耗等多方面的設計需求,非常適合智能接口、機器視覺和人工智能等眾多應用。

如上所述,Xilinx提供許多可編程器件產品,性能和功能從中等到極高都有。這些產品范圍從傳統的FPGA到SoC(具有單個硬核心處理器的FPGA可編程結構)、MPSoC(具有多個硬核心處理器的FPGA可編程結構)、RFSoC(具有RF功能的MPSoC)和ACAP(自適應計算加速平臺)。

為了幫助設計人員使用這些器件來構建設計,Xilinx提供了一套工具來滿足硬件開發人員 (Vivado)、軟件開發人員 (Vitis) 以及AI和數據科學家 (Vitis AI) 的需求。

XC5VFX70T-1FFG665I

XC5VFX30T-3FFG665I

XC5VFX30T-1FFG665I

XC5VFX70T-1FFG665C

XC5VFX100T-1FFG1136I

XC5VFX200T-1FFG1738I

XC5VFX100T-2FFG1738C

XC7Z100-1FF900I

XC7Z100-1FF900C

XC7Z100-2FFG900E

XC7Z100-3FFG900I

XC7Z100-L2FFG900I

XC7Z100-2FFG1156I