引言:在上一篇文章中,我們介紹了DCI的一些理論知識,本文我們重點介紹一下內容:

7系列FPGA DCI使用規則 DCI在HSTL和SSTL I/O標準中的使用舉例

1.7系列FPGA DCI I/O標準

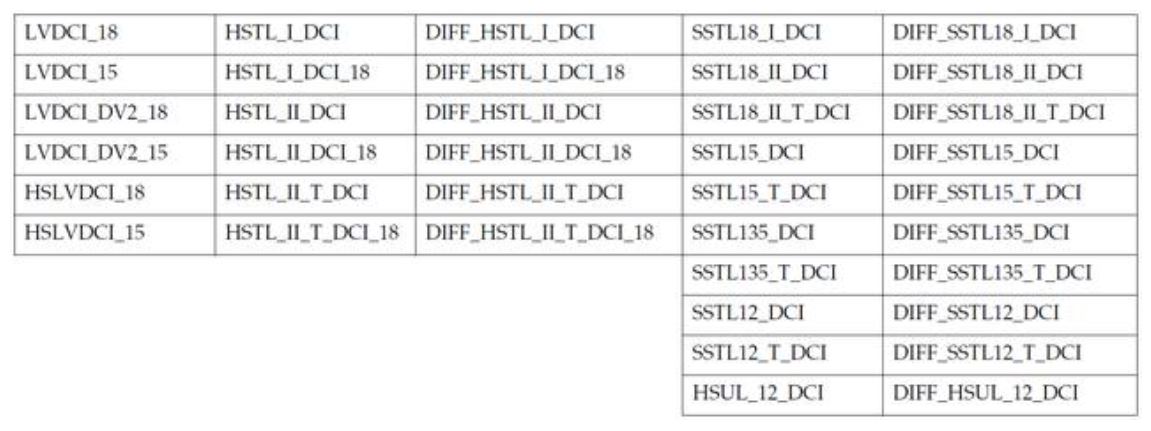

7系列FPGA所有DCI I/O標準如圖1所示。

圖1、系列FPGA所有DCI I/O標準

為了在7系列FPGA中正確使用DCI:

1)基于I/O bank所使用的IOSTANDARDs,VCCO管腳必須連接到恰當的VCCO電壓;

2)正確的DCI I/O緩沖器必須在軟件中使用,可以通過使用IOSTANDARD屬性或者在HDL代碼中例化;

3)DCI標準要求連接外部參考電阻到多功能管腳(VRN和VRP)。當VRN和VRP連接外部參考電阻后,則這兩個管腳則不能用作一般用途I/O。管腳VRN必須通過參考電阻上拉到VCCO,管腳VRP必須通過參考電阻下拉到GND。在DCI級聯應用中,從DCI I/O bank的VRN和VRP管腳無需連接外部參考電阻,可以用作一般用途I/O。

帶有控制阻抗驅動器DCI標準可以用在只作為輸入的信號管腳。對于這種情況,如果這些管腳在給定的I/O bank內是唯一使用DCI的管腳,則該bank不要求連接外部參考電阻到VRN和VRP管腳,此時,該bnak內的VRN和VRP管腳可以用作一般用途I/O。

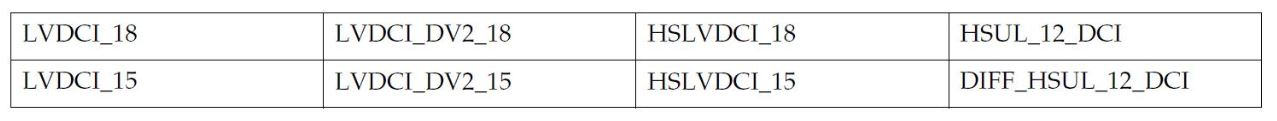

DCI輸入不要求外部參考電阻連接至VRN和VRP的I/O標準如圖2所示。

圖2、DCI輸入不要求外部參考電阻連接至VRN和VRP的I/O標準

4)外部參考電阻的取值應該根據想要的輸出驅動器阻抗或者分立端接阻抗進行選擇。例如,如果使用LVDCI_15,為了達到50Ω輸出驅動器阻抗,VRN和VRP管腳分別連接50Ω參考電阻。當使用SST15_T_DCI標準,為了達到50Ω戴維寧等效端接(R)連接到VCCO/2,外部參考電阻應該為100Ω(2R)。

5)遵循以下DCI I/O bank規則:

當級聯DCI時,對于同一個I/O bank或者一組I/O banks所有輸入,VREF都必須兼容。 同一個bank內的所有輸入、輸出,VCCO必須都兼容。 分立端接、控制阻抗驅動器和半阻抗阻控制驅動器可以在同一bank中共存。

2.DCI使用舉例

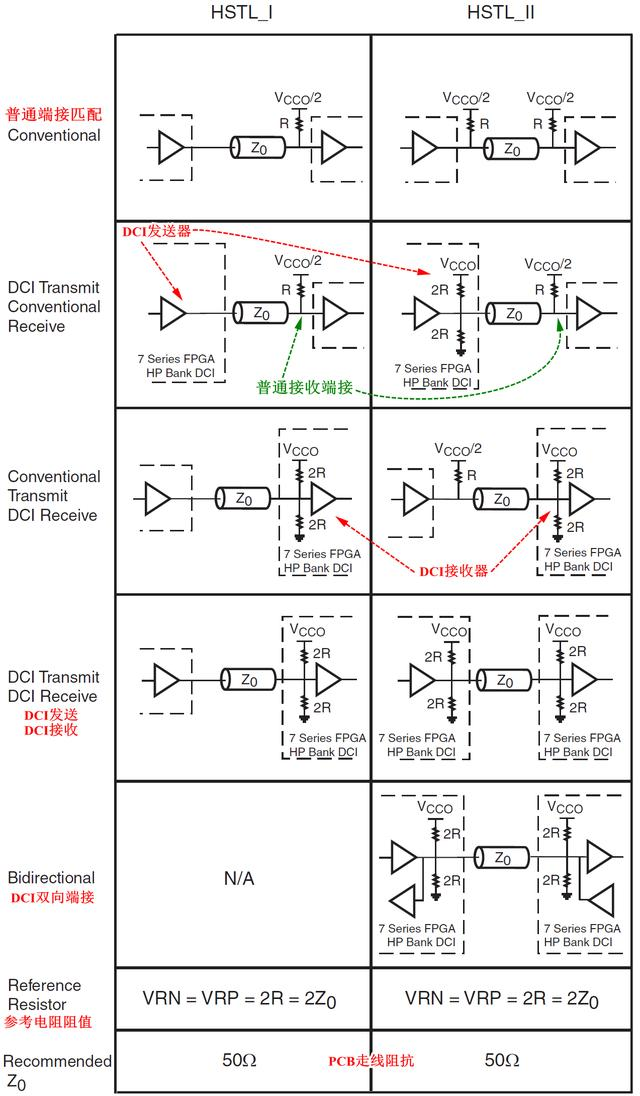

圖3舉例了HSTL_I_DCI和HSTL_II_DCI I/O標準使用。

圖3、HSTL DCI使用舉例

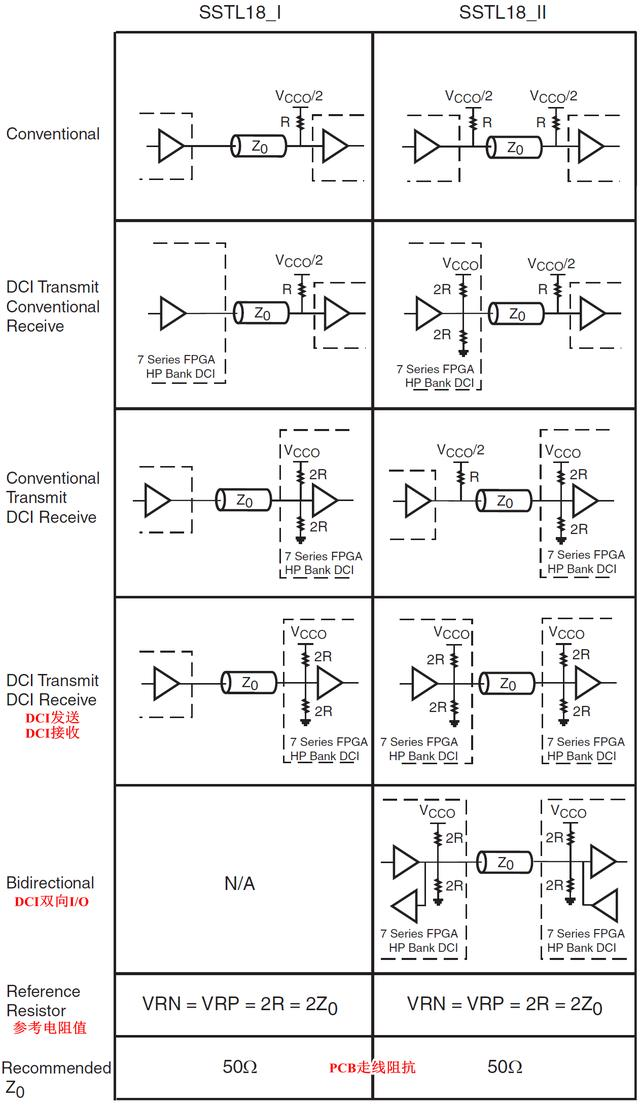

SSTL DCI使用舉例如圖4所示。

圖4、SSTL DCI使用舉例

XC4VFX100-10FFG1152I

XCVU095-2FFVD1517I

XCVU095-2FFVC2104E

XCVU095-1FFVB2104I

XCVU095-2FFVC2104I

XCVU095-2FFVD1517E

XCVU095-1FFVC2104E

XC6VLX550T-2FF1759C

XC6VLX760-3FFG1760C

XC6VLX365T-1FF1156I

XC6VLX760-2FFG1760C

XC6VLX240T-3FFG1759C

XC6VLX240T-1FFG1156C

XC6VLX365T-2FFG1156C

XC6VLX550T-3FFG1759C

XC6VLX240T-L1FFG1759I