類別:微處理器 - MPU

類別:微處理器 - MPU

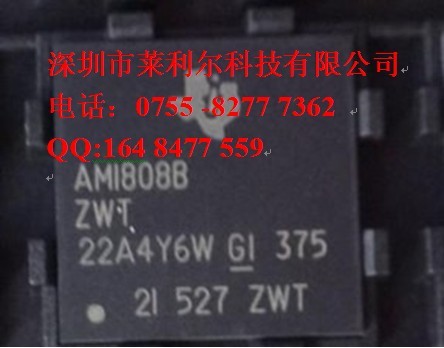

型號:AM1808BZWT3

數據總線寬度: 32 bit最大時鐘頻率: 375 MHz

程序存儲器大小: 64 kB

數據 RAM 大小: 168 KB

接口類型: I2C, SPI, UART

工作電源電壓: 1.2 V

最大工作溫度: + 90 C

半導體產業正在轉換到3D結構,進而導致關鍵薄膜層對高速原子層沉積(ALD)的需求日益升高。過去在平面元件中雖可使用幾個 PVD 與 CVD 步驟,但就閘極堆疊的觀點而言,過渡到 FinFET 元件將需要全方位的 ALD 解決方案。

就 FinFET 而言,以其尺寸及控制關鍵元件參數對后閘極 (gate last) 處理的需求來說,在 14 奈米制程必需用到全 ALD 層。

ALD 對于鉿薄膜沉積的厚度限制為何?

AM1808BZWT3 由于低溫沉積、薄膜純度以及絕佳覆蓋率等固有優點,ALD 早從 21 世紀初即開始應用于半導體制造。 DRAM 電容的高 k 介電質沉積已率先采用此技術,但近來 ALD 在其它半導體制程領域已發展出愈來愈廣泛的應用。高 k 閘極介電質及金屬閘極之 ALD 沉積于先進邏輯晶片已成為標準,并且本技術正用于沉積間隔定義之雙倍暨四倍微影圖樣 (SDDP, SDQP),用以推廣傳統浸潤式微影之使用以界定高密度邏輯暨記憶體設計之最小特征尺寸。

有趣的是,使用 FinFET 減緩了效能提升對介電質 EOT 縮放的需求,并且可用較緩慢的速度調整閘極介電質厚度。二氧化鉿(HfO2)的厚度于最新一代的元件已縮小至 15 埃以下,再進一步的物理縮放將會導致層形成不完全;對于二氧化鉿之縮放,10 至 12 埃 似乎已達到極限。然而,利用能提升閘極堆疊 k 值并且能使用實體較厚層之添加元素,本材料可預期延續使用于更多代制程,藉以降低穿隧漏電流。