這個壓降ΔU會對ADC產生什么樣的影響呢

發布時間:2017/6/14 21:32:05 訪問次數:557

這個壓降ΔU會對ADC產生什么樣的影響呢?也許會有人認為ADC中數字電路和模擬電路是兩個相互隔離的電路,而且電平互不參考。 MAX724CCK實際上,數字電路與模擬電路之間寄生電容及磁珠的存在,已使兩部分電路相互關聯,因此Δσ的產生必然對ADC的正常工作產生影響。測試中發現,將ADC兩邊的數字地和模擬地用導線單點互連,可以通過±6kⅤ的靜電放電測試。這是因為單點互連后Δσ大大降低。

ADC數字地與模擬地之間用磁珠連接是I程師在電路設計中經常發生的錯誤,這些錯誤首先來自ADC電源引腳和接地引腳的名稱。模擬地和數字地的引腳名稱表示內部元件本身的作用,但是未必意味著外部也應該按照內部作用去做。ADC集成電路內部有模擬電路和數字電路兩部分,為了避免數字信號耦合到模擬電路中去,模擬地和數字地通常分開,如圖2.91所示的ADC。但是從芯片上的焊點到封裝引腳的連線所產生的引線接合電感和電阻,并不是℃設計者專門加上去的。快速變化的數字電流在B點產生一個電壓,經過寄生

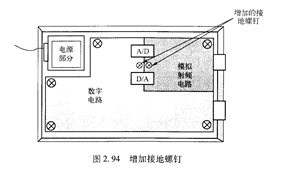

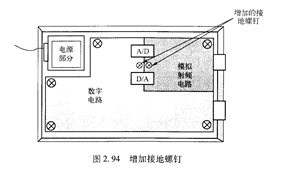

電容必然耦合到模擬電路的A點。可見,在數字地與模擬地之間串聯磁珠并不能減小數字電路的噪聲向模擬電路傳輸,而且任何在數字地引腳附加的外部阻抗都將在B點上引起較大的數字噪聲,然后,大的數字噪聲通過雜散電容耦合到模擬電路上。芯片內部雜散電容產生的耦合是制造芯片過程中IC設計者應考慮的問題。為了防止進一步耦合,需要模擬地和數字地的引腳在外面用最短的連線接到同一個低阻抗的接地平面上。本案例中金屬外殼的底板實際上提供一個低阻抗的接地平面,但PCB與金屬底板的連接點離ADC太遠,高頻下,對于ADC的兩個地引腳來講,并不能實現低阻抗接地。如果再在ADC附近增加兩個接地點,一個在模擬電路側,另一個在數字電路側,如圖2.%所示,將大大增強接地效果。

這個壓降ΔU會對ADC產生什么樣的影響呢?也許會有人認為ADC中數字電路和模擬電路是兩個相互隔離的電路,而且電平互不參考。 MAX724CCK實際上,數字電路與模擬電路之間寄生電容及磁珠的存在,已使兩部分電路相互關聯,因此Δσ的產生必然對ADC的正常工作產生影響。測試中發現,將ADC兩邊的數字地和模擬地用導線單點互連,可以通過±6kⅤ的靜電放電測試。這是因為單點互連后Δσ大大降低。

ADC數字地與模擬地之間用磁珠連接是I程師在電路設計中經常發生的錯誤,這些錯誤首先來自ADC電源引腳和接地引腳的名稱。模擬地和數字地的引腳名稱表示內部元件本身的作用,但是未必意味著外部也應該按照內部作用去做。ADC集成電路內部有模擬電路和數字電路兩部分,為了避免數字信號耦合到模擬電路中去,模擬地和數字地通常分開,如圖2.91所示的ADC。但是從芯片上的焊點到封裝引腳的連線所產生的引線接合電感和電阻,并不是℃設計者專門加上去的。快速變化的數字電流在B點產生一個電壓,經過寄生

電容必然耦合到模擬電路的A點。可見,在數字地與模擬地之間串聯磁珠并不能減小數字電路的噪聲向模擬電路傳輸,而且任何在數字地引腳附加的外部阻抗都將在B點上引起較大的數字噪聲,然后,大的數字噪聲通過雜散電容耦合到模擬電路上。芯片內部雜散電容產生的耦合是制造芯片過程中IC設計者應考慮的問題。為了防止進一步耦合,需要模擬地和數字地的引腳在外面用最短的連線接到同一個低阻抗的接地平面上。本案例中金屬外殼的底板實際上提供一個低阻抗的接地平面,但PCB與金屬底板的連接點離ADC太遠,高頻下,對于ADC的兩個地引腳來講,并不能實現低阻抗接地。如果再在ADC附近增加兩個接地點,一個在模擬電路側,另一個在數字電路側,如圖2.%所示,將大大增強接地效果。

上一篇:碳膜電阻體會因電流過大而嚴重燒壞

上一篇:按照以上的分析及測試結果

公網安備44030402000607

公網安備44030402000607