首先對框體的背板和主控制板的PCB進行詳細的檢查

發布時間:2017/6/26 19:51:10 訪問次數:458

【原因分析】

為了確定輻射源的耦合途徑,首先對框體的背板和主控制板的PCB進行詳細的檢查。LM139J/883通過對背板及主控制板的PCB布線檢查,發現干擾信號耦合到電源線的途徑和原Fkl有以下 幾種可能:

(1)背板上主控制板槽位的時鐘布線離框體供電電源-48地較近,同時與背板DGND的隔離距離為~sO mil,可能會耦合到電源線。

(2)時鐘線布線是采用兩端匹配的方式,通過上拉電阻匹配到Ⅴ"電源層。時鐘信號輸出原理圖如圖6。⒛所示。

如果Ⅴm濾波電容選擇的不合理,則可能會將十擾傳人Ⅴ1T層,而Ⅴm層與-48Ⅴ電源層在主控制板上有較大面積的重合,-鯧Ⅴ電源層很有可能被耦合到干擾。 .

經過以上的初步分析,可按以下步驟定位測試: 優化框體背板的時鐘匹配電阻的濾波電容,改為0.1uF和0.u2uF。

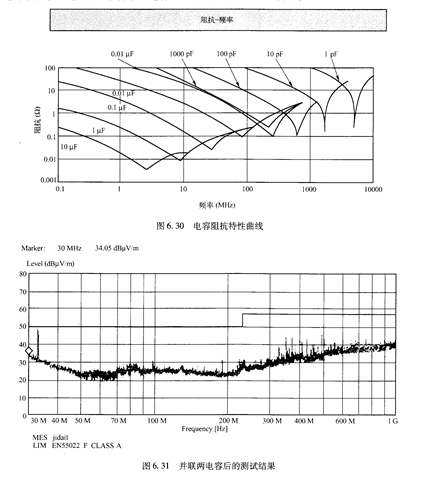

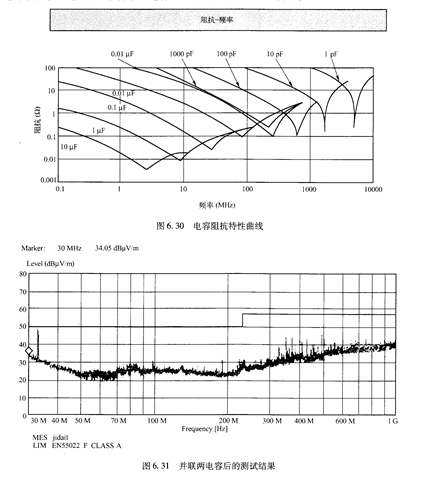

由圖6.30所示的電容阻抗特性曲線可知,兩電容并聯后的濾波范圍在幾十兆赫茲之間。修改完后,再進行測試,并聯兩電容后的測試結果如圖6.31所示。

圖6.31中的測試結果與以前的測試結果相比有改善,說明干擾與Ⅴη電源層有關,但是耦合發生在背板還是主控制板,需要進一步定位。

步驟二

利用專門加工的接插件將主控制板輸出的32.768MHz時鐘上拉到Vm,然后啟動主控制板,通過接插件上拉的原理圖如圖6.32所示。

【原因分析】

為了確定輻射源的耦合途徑,首先對框體的背板和主控制板的PCB進行詳細的檢查。LM139J/883通過對背板及主控制板的PCB布線檢查,發現干擾信號耦合到電源線的途徑和原Fkl有以下 幾種可能:

(1)背板上主控制板槽位的時鐘布線離框體供電電源-48地較近,同時與背板DGND的隔離距離為~sO mil,可能會耦合到電源線。

(2)時鐘線布線是采用兩端匹配的方式,通過上拉電阻匹配到Ⅴ"電源層。時鐘信號輸出原理圖如圖6。⒛所示。

如果Ⅴm濾波電容選擇的不合理,則可能會將十擾傳人Ⅴ1T層,而Ⅴm層與-48Ⅴ電源層在主控制板上有較大面積的重合,-鯧Ⅴ電源層很有可能被耦合到干擾。 .

經過以上的初步分析,可按以下步驟定位測試: 優化框體背板的時鐘匹配電阻的濾波電容,改為0.1uF和0.u2uF。

由圖6.30所示的電容阻抗特性曲線可知,兩電容并聯后的濾波范圍在幾十兆赫茲之間。修改完后,再進行測試,并聯兩電容后的測試結果如圖6.31所示。

圖6.31中的測試結果與以前的測試結果相比有改善,說明干擾與Ⅴη電源層有關,但是耦合發生在背板還是主控制板,需要進一步定位。

步驟二

利用專門加工的接插件將主控制板輸出的32.768MHz時鐘上拉到Vm,然后啟動主控制板,通過接插件上拉的原理圖如圖6.32所示。

上一篇:時鐘噪聲耦合到電源的原理

公網安備44030402000607

公網安備44030402000607