ңПІЫМоідјјРg

°lІј•rйg:2017/10/12 22:03:36 ФLҶ–ҙО”ө:940

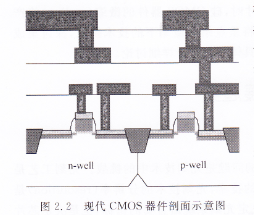

ҲD2.2КЗ¬FҙъCMC)SЖчјюЖКГжөДКҫТвҲDЎЈТ»°гҒнХf,Л®ЖҪ·ҪПтөДіЯҙзОўҝs·щ¶ИұИҙ№Цұ·ҪПтөД·щ¶Иёьҙу,PT4213Я@ҢўҢ§ЦВңПІЫ(°ьә¬ҪУУ|ҝЧ)өДЙоҢ’ұИ(aspect mtio)ТІлSЦ®МбёЯ,һйұЬГвңП ІЫМоідЯ^іМЦР®aЙъҝХСЁ(void),ңПІЫөДМоідЎчЛҮјјРgТІІ»”а°lХ№ЎЈҸДҲDЦРҝЙТҠ,јҜіЙлҠВ·РҫЖ¬өДЦЖФмЯ^іМЦР°ьә¬әЬ¶а·NМоідјјРgЙПөДМф‘р,°ьАЁң\ңПІЫёфлxЎўҪУУ|ҝЧәНңПІЫЎЈёщ“юМоідІДБПөДІ»Н¬,Моід№ӨЛҮЦчТӘ·ЦһйҪ^ҫүҪйЩ|өДМоідјјРgәНҢ§лҠІДБПөДМоідјјРgЎЈ

ФЪҙуУЪ0.8umөДйgП¶ЦРМоідҪ^ҫүҪйЩ|•r,ЖХұйІЙУГөИлxЧУуwФцҸҠ»ҜҢWҡвПаіБ·e(PlasmaEnhanced Chemical Vapor Deposition,PECVD);И»¶шҢҰУЪРЎУЪ0.8umөДйgП¶,УГҶОІҪPECVD№ӨЛҮМоідҶ–П¶•r•юФЪЖдЦРІҝ®aЙъҝХСЁЎЈPECVDјј РgјУЙПіБ·eәҘШЦОgТ»іБ·e№ӨЛҮұ»УГТФМоід0.5~0,8umөДйgП¶,ТІҫНКЗХf,ФЪіхКјіБ·eНкіЙІҝ·ЦМоҝЧЙРОҙ°lЙъҠA”а•rҫoёъЦшЯMРРҝМОg№ӨЛҮТФЦШРВҙтй_йgП¶ИЛҝЪ,Ц®әуФЩҙОіБ·eТФНкіЙҢҰ

ХыӮҖйgП¶өДМоід[5]ЎЈёЯГЬ¶ИөИлxЧУ(High Density Plasn1a,HDP)»ҜҢWҡвПаіБ·eјјРgЎчЛҮФЪН¬Т»ӮҖ·ҙ‘ӘЗ»(chamber)ЦРФӯО»өШЯMРРіБ·eәНҝМОgөД№ӨЛҮ,НЁЯ^ҝШЦЖйgП¶өД№ХҪЗМҺіБ·eҝМОgұИ(depositionctch ratio),К№өГғфіБ·eЛЩВКҪУҪьБг,ҸД¶шМбёЯЖдМоідДЬБҰЎЈФ“јјРgДЬүтЯm‘ӘЙоҢ’ұИФЪ6:1ЧуУТөДРиЗу,ІўқMЧг90nmјјРg№қьcөДРиЗуЎЈ

ҲD2.2КЗ¬FҙъCMC)SЖчјюЖКГжөДКҫТвҲDЎЈТ»°гҒнХf,Л®ЖҪ·ҪПтөДіЯҙзОўҝs·щ¶ИұИҙ№Цұ·ҪПтөД·щ¶Иёьҙу,PT4213Я@ҢўҢ§ЦВңПІЫ(°ьә¬ҪУУ|ҝЧ)өДЙоҢ’ұИ(aspect mtio)ТІлSЦ®МбёЯ,һйұЬГвңП ІЫМоідЯ^іМЦР®aЙъҝХСЁ(void),ңПІЫөДМоідЎчЛҮјјРgТІІ»”а°lХ№ЎЈҸДҲDЦРҝЙТҠ,јҜіЙлҠВ·РҫЖ¬өДЦЖФмЯ^іМЦР°ьә¬әЬ¶а·NМоідјјРgЙПөДМф‘р,°ьАЁң\ңПІЫёфлxЎўҪУУ|ҝЧәНңПІЫЎЈёщ“юМоідІДБПөДІ»Н¬,Моід№ӨЛҮЦчТӘ·ЦһйҪ^ҫүҪйЩ|өДМоідјјРgәНҢ§лҠІДБПөДМоідјјРgЎЈ

ФЪҙуУЪ0.8umөДйgП¶ЦРМоідҪ^ҫүҪйЩ|•r,ЖХұйІЙУГөИлxЧУуwФцҸҠ»ҜҢWҡвПаіБ·e(PlasmaEnhanced Chemical Vapor Deposition,PECVD);И»¶шҢҰУЪРЎУЪ0.8umөДйgП¶,УГҶОІҪPECVD№ӨЛҮМоідҶ–П¶•r•юФЪЖдЦРІҝ®aЙъҝХСЁЎЈPECVDјј РgјУЙПіБ·eәҘШЦОgТ»іБ·e№ӨЛҮұ»УГТФМоід0.5~0,8umөДйgП¶,ТІҫНКЗХf,ФЪіхКјіБ·eНкіЙІҝ·ЦМоҝЧЙРОҙ°lЙъҠA”а•rҫoёъЦшЯMРРҝМОg№ӨЛҮТФЦШРВҙтй_йgП¶ИЛҝЪ,Ц®әуФЩҙОіБ·eТФНкіЙҢҰ

ХыӮҖйgП¶өДМоід[5]ЎЈёЯГЬ¶ИөИлxЧУ(High Density Plasn1a,HDP)»ҜҢWҡвПаіБ·eјјРgЎчЛҮФЪН¬Т»ӮҖ·ҙ‘ӘЗ»(chamber)ЦРФӯО»өШЯMРРіБ·eәНҝМОgөД№ӨЛҮ,НЁЯ^ҝШЦЖйgП¶өД№ХҪЗМҺіБ·eҝМОgұИ(depositionctch ratio),К№өГғфіБ·eЛЩВКҪУҪьБг,ҸД¶шМбёЯЖдМоідДЬБҰЎЈФ“јјРgДЬүтЯm‘ӘЙоҢ’ұИФЪ6:1ЧуУТөДРиЗу,ІўқMЧг90nmјјРg№қьcөДРиЗуЎЈ

ҹбйTьc“ф

ҹбйTьc“ф

- CVDКЗУГҒнЦЖӮд¶юСх»Ҝ№иҪйЩ|ұЎДӨөДЦчТӘ№ӨЛҮ·Ҫ

- лҠЧУ®aЖ·СbЕдЯ^іМЦРіЈУГөДҲDјҲУРДДР©?

- ЭdБчЧУЯwТЖВКМбёЯјјРg

- ұЎҢУҪрҢЩіБ·eРиТӘБјәГөДЕ_лAёІЙwРФ

- МмҫҖҫалxөШЖҪГжөДёЯ¶И‘ӘФЪТҺ¶ЁөД·¶ҮъғИЧғ»Ҝ

- лҠБч·ө»ШөДЧоөНЧиҝ№НЁөАІў·ЗКЗЧо¶МВ·ҸҪёЯ

- һйұЬГвёЯоlРЕМ–НЁЯ^PCBЧЯҫҖ•r®aЙълҠҙЕЭ—Йд

- РЕМ–өДЯ…СШЛЩВКТІКЗФҪҒнФҪҝм

- №ӨЛҮОДјюөД№ЬАнТӘЗу

- јҜіЙлҠВ·өДЧR„eЕcҷzңy

НЖЛ]јјРgЩYБП

НЖЛ]јјРgЩYБП

- ҳIУа—lјюПВPCM2702

- PGM2702ІЙУГSSOP28·вСbЈ¬ТэД_РЎ¶шГЬЈ¬EP3... [Ф”јҡ]

- ДЈ”MәН»мәПРЕМ–ЖҪЕ_TreoФ”Зй

- PXIәНLXIДЈүK»ҜҪвӣQ·Ҫ°ёҪвЧx

- AN-13-0004_CANКХ°lЖчҪYҳӢ…ў”өМШ

- ЖБұО–ЕІЫңПјјРg (SGT)&#

- өЪТ»ҙъSGT MOSFETПөБРјјРgҪYҳӢ…ў”ө·в

- И«ЗтКЧоwGSE DPUРҫЖ¬°lІј

- ¶аГҪуw…fМҺАнЖчSM501ФЪЗ¶ИлКҪПөҪyЦРөД‘ӘУГ

- »щУЪIEEE802.11bөДEPAңШ¶ИЧғЛНЖч

- QUICCEngineРВТэЗжНЖ„УIPҫWҪjёпРВ

- SoCГжКА°ЛДкәуөД®aҳIҷCУц

- MPC8xxПөБРМҺАнЖчөДЗ¶ИлКҪПөҪyлҠФҙФOУӢ

- dsPICј°ЖдФЪҪ»БчЧғоlХ{ЛЩЦРөД‘ӘУГСРҫҝ

№«ҫW°ІӮд44030402000607

№«ҫW°ІӮд44030402000607