印制電路板的抗干擾設計

發布時間:2017/12/18 20:44:47 訪問次數:405

在印制電路板的設計中,為了使所設計的產品能夠更好、更有效地工作,必須考慮它的抗干擾能力。印制電路板的抗干擾設計與具體電路有著密切的關系,這里僅就幾項常用措施做一些說明。

1.地線設計 NBB-302-E

電路中接地點的概念表示零電位,其他電位均是相對于這一點而言的。在實際的印制電路板上,地線并不能保證是絕對零電位,往往存在一個很小的非零電位值。由于電路中的放大作用,這個小小的電位便可能產生影響電路性能的干擾――地線共阻抗干擾。

消除地線共阻抗干擾的方法主要有以下幾種。

1)盡量加粗接地線

若接地線很細,接地電位則會隨電流的變化而變化,致使電子設備的定時信號電平不穩,抗噪聲性能變壞。因此,應將接地線盡量加粗,使它能通過3倍于印制電路板的允許電流。如果有可能,接地線的寬度應大于3mm。

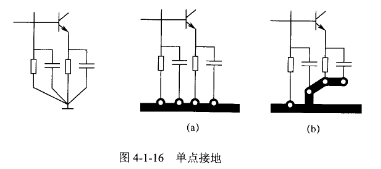

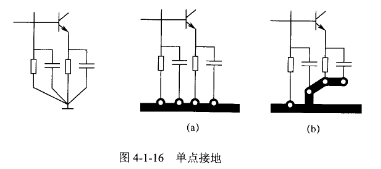

2)單J點接地

單點接地(也稱一點接地)是消除地線干擾的基本原則,即將電路中本單元 (級)的各接地元器件盡可能就近接到公共地線的一段或一個區域里,如圖⒋⒈16(a)所示;也可以接到一個分支地線上,如圖⒋⒈I6(b)所示。

在印制電路板的設計中,為了使所設計的產品能夠更好、更有效地工作,必須考慮它的抗干擾能力。印制電路板的抗干擾設計與具體電路有著密切的關系,這里僅就幾項常用措施做一些說明。

1.地線設計 NBB-302-E

電路中接地點的概念表示零電位,其他電位均是相對于這一點而言的。在實際的印制電路板上,地線并不能保證是絕對零電位,往往存在一個很小的非零電位值。由于電路中的放大作用,這個小小的電位便可能產生影響電路性能的干擾――地線共阻抗干擾。

消除地線共阻抗干擾的方法主要有以下幾種。

1)盡量加粗接地線

若接地線很細,接地電位則會隨電流的變化而變化,致使電子設備的定時信號電平不穩,抗噪聲性能變壞。因此,應將接地線盡量加粗,使它能通過3倍于印制電路板的允許電流。如果有可能,接地線的寬度應大于3mm。

2)單J點接地

單點接地(也稱一點接地)是消除地線干擾的基本原則,即將電路中本單元 (級)的各接地元器件盡可能就近接到公共地線的一段或一個區域里,如圖⒋⒈16(a)所示;也可以接到一個分支地線上,如圖⒋⒈I6(b)所示。

熱門點擊

熱門點擊

- 應力遷移

- 電壓斜坡(V-ramp)和電流斜坡(J-ra

- 焊錫絲的拿法

- oBIRCH/XIⅤA案例分析

- 按集成規模分類

- 發射極和集電極的判別

- 擴散法制備pn結是利用擴散爐

- 錫焊的機理

- 波形存儲器在這里也叫正弦查找表

- OBIRCH雷射注入技術在90nm制程失效分

推薦技術資料

推薦技術資料

- 單片機版光立方的制作

- N視頻: http://v.youku.comN_sh... [詳細]

公網安備44030402000607

公網安備44030402000607