THS4631DRG4 數字波形大多數將畫成理想波形

發布時間:2020/1/16 12:33:24 訪問次數:853

數字電路的分析、設計與測試,數字電路的分析方法.

數字電路處理的是數字信號,電路中的半導體器件工作在開關狀態,例如晶體管王作在飽和區或截止區,所以不能采用模擬電路的分析方法,例如小信號模型分析法。數字電路又稱為邏輯電路,在電路結構、功能和特點等方面均不同于模擬電路,主要研究的對象是電路的輸出與輸人之間的邏輯關系,因而,數字電路的分析方法與模擬電路完全不同,所采用的分析工具是邏輯代數,表達電路輸出與輸入的關系主要用真值表、功能表、邏輯表達式或波形圖。

隨著計算機技術的發展,借助計算機仿真軟件,可以更直觀、更快捷、更全面地對電路進行分析。不僅可以對數字電路,而且可以對數模混合電路進行仿真分析;不僅可以進行電路的功能仿真,顯示邏輯仿真的波形結果,以檢查邏輯錯誤,而且可以考慮器件及連線的延遲時間,進行時序仿真,檢測電路中存在的冒險競爭、時序錯誤等問題。

數字電路的設計方法,數字電路的設計是從給定的邏輯功能要求出發,確定輸人、輸出變量,選擇適當的邏輯器件,設計出符合要求的邏輯電路。設計過程一般有方案的提出、驗證和修改三個階段。設計方式分為傳統的設計方式和基于EDA①軟件的設計方式。傳統的硬件電路設計全過程都是由人工完成,硬件電路的驗證和調試是在電路構成后進行的,電路存在的問題只能在驗證后發現。如果存在的問題較大,有可能重新設計電路,因而設計周期長,資源浪費大,不能滿足大規模集成電路設計的要求。基于王pA軟件的設計方式是借助于計算機來快速準確地完成電路的設計。設計者提出方案后,利用計算機進行邏輯分析、性能分析、時序測試,如果發現錯誤或方案不理想,可以重復上述過程直至得到滿意的電路,然后進行硬件電路的實現。這種方法提高了設計質量,縮短了設計周期,節省了設計費用,提高了產品的競爭力。因此EDA軟件已成為設計人員不可缺少的有力工具。

EDA軟件的種類較多,大多數軟件包含以下主要工具:

原理圖輸人 設計者可以如同在紙上畫電路一樣,將邏輯電路圖輸入到計算機,軟件自動檢查電路的接線、電源及地線的連接、信號的連接等。

EDA系Elcctronic Design Automauon的縮寫。

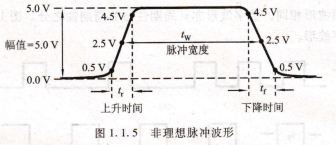

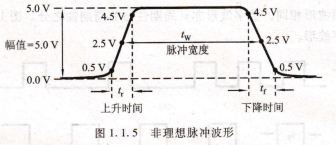

數字邏輯概論,分別用上升時間rr和下降時間莎r描述,如圖1.1.5所示。將脈沖幅值的10%到90%時所經歷的時間稱為上升時間rr。下降時間則相反,從脈沖幅值的90%下降到10%時所經歷的時間稱為下降時間tf0將脈沖幅值的50%的兩個時間點所跨越的時間稱為脈沖寬度Jw,對于不同類型的器件和電路,其上升和下降時間各不相同。一般數字信號上升和下降時間的典型值約為幾納秒(ns)。

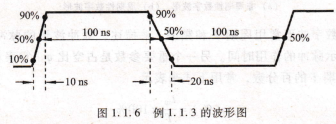

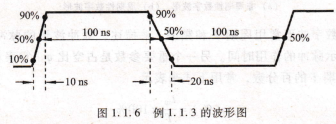

幅值=⒌OV,脈沖寬度,上升時間下降時間,非理想脈沖波形,例1.1-3 試繪出一脈沖波形,設它的占空比為50%,脈沖寬度為100 ns,上升時間為10 ns,而下降時間為20 ns。

解:根據題意,所繪出的脈沖波形如圖1.1.6所示。

本書所用的數字波形大多數將畫成理想波形。實際上,每一波形均有上升時間和下降時間。由于rr和Jf與脈沖寬度的時間相比非常小,則不必在每一波形上表示出來。畫波形的目的只是為了知道高、低電平所經歷的時間。

時序圖,在數字電路中,常用時序圖或稱為脈沖波形圖,來分析時序電路的邏輯功能。表明各信號之間時序關系的波形圖稱為時序圖。為一典型的時序圖。圖中CP為時鐘脈沖信號,它是數字系統中的時間參考信號。地址線、片選和數據寫入等信號亦示于中。關于時序圖中各個波形的具體作用,將在后續章節中介紹。通常數字集成電路,例如存儲器和時序邏輯器件等均須附有時序圖,以便于進行數字系統的分析、設計和應用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

數字電路的分析、設計與測試,數字電路的分析方法.

數字電路處理的是數字信號,電路中的半導體器件工作在開關狀態,例如晶體管王作在飽和區或截止區,所以不能采用模擬電路的分析方法,例如小信號模型分析法。數字電路又稱為邏輯電路,在電路結構、功能和特點等方面均不同于模擬電路,主要研究的對象是電路的輸出與輸人之間的邏輯關系,因而,數字電路的分析方法與模擬電路完全不同,所采用的分析工具是邏輯代數,表達電路輸出與輸入的關系主要用真值表、功能表、邏輯表達式或波形圖。

隨著計算機技術的發展,借助計算機仿真軟件,可以更直觀、更快捷、更全面地對電路進行分析。不僅可以對數字電路,而且可以對數模混合電路進行仿真分析;不僅可以進行電路的功能仿真,顯示邏輯仿真的波形結果,以檢查邏輯錯誤,而且可以考慮器件及連線的延遲時間,進行時序仿真,檢測電路中存在的冒險競爭、時序錯誤等問題。

數字電路的設計方法,數字電路的設計是從給定的邏輯功能要求出發,確定輸人、輸出變量,選擇適當的邏輯器件,設計出符合要求的邏輯電路。設計過程一般有方案的提出、驗證和修改三個階段。設計方式分為傳統的設計方式和基于EDA①軟件的設計方式。傳統的硬件電路設計全過程都是由人工完成,硬件電路的驗證和調試是在電路構成后進行的,電路存在的問題只能在驗證后發現。如果存在的問題較大,有可能重新設計電路,因而設計周期長,資源浪費大,不能滿足大規模集成電路設計的要求。基于王pA軟件的設計方式是借助于計算機來快速準確地完成電路的設計。設計者提出方案后,利用計算機進行邏輯分析、性能分析、時序測試,如果發現錯誤或方案不理想,可以重復上述過程直至得到滿意的電路,然后進行硬件電路的實現。這種方法提高了設計質量,縮短了設計周期,節省了設計費用,提高了產品的競爭力。因此EDA軟件已成為設計人員不可缺少的有力工具。

EDA軟件的種類較多,大多數軟件包含以下主要工具:

原理圖輸人 設計者可以如同在紙上畫電路一樣,將邏輯電路圖輸入到計算機,軟件自動檢查電路的接線、電源及地線的連接、信號的連接等。

EDA系Elcctronic Design Automauon的縮寫。

數字邏輯概論,分別用上升時間rr和下降時間莎r描述,如圖1.1.5所示。將脈沖幅值的10%到90%時所經歷的時間稱為上升時間rr。下降時間則相反,從脈沖幅值的90%下降到10%時所經歷的時間稱為下降時間tf0將脈沖幅值的50%的兩個時間點所跨越的時間稱為脈沖寬度Jw,對于不同類型的器件和電路,其上升和下降時間各不相同。一般數字信號上升和下降時間的典型值約為幾納秒(ns)。

幅值=⒌OV,脈沖寬度,上升時間下降時間,非理想脈沖波形,例1.1-3 試繪出一脈沖波形,設它的占空比為50%,脈沖寬度為100 ns,上升時間為10 ns,而下降時間為20 ns。

解:根據題意,所繪出的脈沖波形如圖1.1.6所示。

本書所用的數字波形大多數將畫成理想波形。實際上,每一波形均有上升時間和下降時間。由于rr和Jf與脈沖寬度的時間相比非常小,則不必在每一波形上表示出來。畫波形的目的只是為了知道高、低電平所經歷的時間。

時序圖,在數字電路中,常用時序圖或稱為脈沖波形圖,來分析時序電路的邏輯功能。表明各信號之間時序關系的波形圖稱為時序圖。為一典型的時序圖。圖中CP為時鐘脈沖信號,它是數字系統中的時間參考信號。地址線、片選和數據寫入等信號亦示于中。關于時序圖中各個波形的具體作用,將在后續章節中介紹。通常數字集成電路,例如存儲器和時序邏輯器件等均須附有時序圖,以便于進行數字系統的分析、設計和應用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607