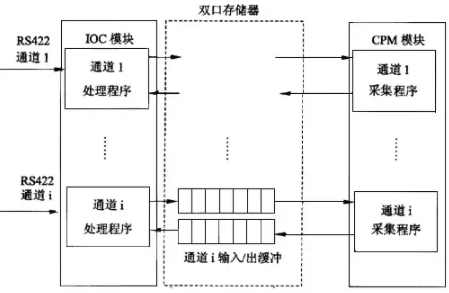

信號的波特率為fb實現CPU之間數據的高速傳輸

發布時間:2022/11/26 19:26:03 訪問次數:188

在5V電源電壓條件下,通信信號電平幅度上升到判別電壓幅度(TTL高電平或CMOS高電平)所需時間是T=-R(C1+C2)ln0.46(對TTL電路)或T=-R(C1+C2)ln0.72(對CMOS電路)。如果信號的波特率為fb,為確保正確接收,信號上升時間應當為信號脈沖寬度的1/4~1/10。

由于ADμC812只提供表貼封裝形式,因而在用仿真器進行程序調試時將會帶來一些問題。為方便調試,ADμC812A片內除集成了各具特色的硬件模塊外,還因化了方便實用的監控調試軟件,使其只需少量的外圍器件即可實現聯機調試,從而大大方便了用戶的使用,縮短了產品的研制周期。

在Neuron芯片中,每個CPU最小周期等于3個系統周期;每個系統時鐘周期等于2個輸入鐘周期;3個CPU的最小周期分別間隔1個系統鐘周期。這樣,每個CPU在1個指令周期內部能訪問存儲區和ALU一次。系統對3個CPU采用了管道技術,在不影響性能的情況下降低硬件的需求。3個CPU可并行工作,不會造成耗時中斷和上下文切換。

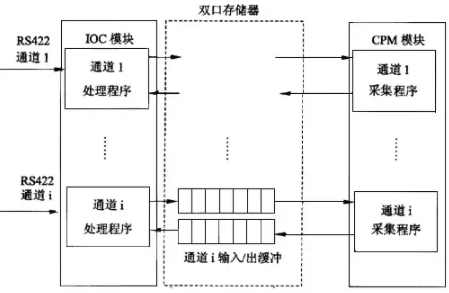

利用這種方法也能夠實現CPU之間數據的高速傳輸,但是,它必須制成專用芯片,把CPU和RAM等元件封裝在一起。因此,這種方法比較適合于特定的工業場合。

隨著總線技術的發展,使得多主多從的單片機系統設計變得越來越簡單。設計者只須通過接口芯片就可以將CPU掛到總線上去,實現CPU之間的通信。

ADμC812在單個芯片內集成了8路12位ADC采集系統、2路12位DAC、80C52MCU內核、8KB的閃速/電可擦除程序存儲器、640字節的閃速/電可擦除數據存儲器、看門狗定時器、640字節的閃速/電可擦除數據存儲器、看門狗定時器、電源監視器、I2C兼容的SPI和標準的UART串行I/O模塊及靈活的電源管理方案等等,真正實現了單片機應用系統的單片機。

限于篇幅其ADC采集子系統及其在系統編程技術。

可編程性是應用系統發展的必然趨勢。為適應不同信號源的實際需求,ADμC812片內ADC模塊內的所有部件都能方便地通過3個SFR寄存器來設置。

上海德懿電子科技有限公司 www.deyie.com

來源:21ic.如涉版權請聯系刪除。圖片供參考

在5V電源電壓條件下,通信信號電平幅度上升到判別電壓幅度(TTL高電平或CMOS高電平)所需時間是T=-R(C1+C2)ln0.46(對TTL電路)或T=-R(C1+C2)ln0.72(對CMOS電路)。如果信號的波特率為fb,為確保正確接收,信號上升時間應當為信號脈沖寬度的1/4~1/10。

由于ADμC812只提供表貼封裝形式,因而在用仿真器進行程序調試時將會帶來一些問題。為方便調試,ADμC812A片內除集成了各具特色的硬件模塊外,還因化了方便實用的監控調試軟件,使其只需少量的外圍器件即可實現聯機調試,從而大大方便了用戶的使用,縮短了產品的研制周期。

在Neuron芯片中,每個CPU最小周期等于3個系統周期;每個系統時鐘周期等于2個輸入鐘周期;3個CPU的最小周期分別間隔1個系統鐘周期。這樣,每個CPU在1個指令周期內部能訪問存儲區和ALU一次。系統對3個CPU采用了管道技術,在不影響性能的情況下降低硬件的需求。3個CPU可并行工作,不會造成耗時中斷和上下文切換。

利用這種方法也能夠實現CPU之間數據的高速傳輸,但是,它必須制成專用芯片,把CPU和RAM等元件封裝在一起。因此,這種方法比較適合于特定的工業場合。

隨著總線技術的發展,使得多主多從的單片機系統設計變得越來越簡單。設計者只須通過接口芯片就可以將CPU掛到總線上去,實現CPU之間的通信。

ADμC812在單個芯片內集成了8路12位ADC采集系統、2路12位DAC、80C52MCU內核、8KB的閃速/電可擦除程序存儲器、640字節的閃速/電可擦除數據存儲器、看門狗定時器、640字節的閃速/電可擦除數據存儲器、看門狗定時器、電源監視器、I2C兼容的SPI和標準的UART串行I/O模塊及靈活的電源管理方案等等,真正實現了單片機應用系統的單片機。

限于篇幅其ADC采集子系統及其在系統編程技術。

可編程性是應用系統發展的必然趨勢。為適應不同信號源的實際需求,ADμC812片內ADC模塊內的所有部件都能方便地通過3個SFR寄存器來設置。

上海德懿電子科技有限公司 www.deyie.com

來源:21ic.如涉版權請聯系刪除。圖片供參考

公網安備44030402000607

公網安備44030402000607