通過紫外固化方法除去造孔劑從而在薄膜內留下納米尺寸孔隙

發布時間:2023/10/3 14:07:46 訪問次數:63

在后端的互連方面,主要的挑戰來自RC延遲,為了降低RC延遲,電介質h值必須隨著技術節點不斷降低。

從180/130nm采用摻氟的氧化硅(FSG)到90/65/40nm采用致密摻碳的氧化硅(SiCOH),再到32nm以后的多孔的摻碳氧化硅(p SiCOH),材料的h值從3,5到3.0~2.7,再到小于2.5。

不僅金屬間電介質,在銅化學機械拋光后的表面沉積介質阻擋層的乃值也必須不斷降低。

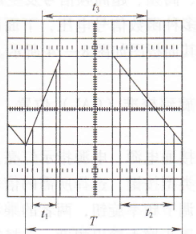

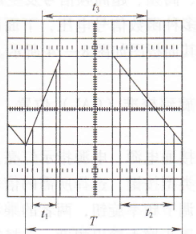

后端的多孔摻碳氧化硅的沉積,在常規的等離子體增強CVD(PECVD)沉積過程中,需要加人造孔劑,然后通過紫外固化的方法除去造孔劑,從而在薄膜內留下納米尺寸的孔隙。

電路環境中檢測氣敏電阻器的方法,根據實測結果可對氣敏電阻器的好壞作出判斷:

將氣敏電阻器放置在電路中,氣敏電阻器檢測到氣體濃度發生變化時所在電路申的電壓參數也應發生變化,否則,多為氣敏電阻器損壞。

在正常情況下,光敏電阻器應有一個固定阻值,所在環境光線變化時,阻值隨之變化,否則多為光敏電阻器異常。

濕敏電阻器的檢測方法與熱敏電阻器的檢測方法相似,不同的是在測過改變濕度條件,用萬用表檢測濕敏電阻器的阻值變化情況判斷好壞,為電路中待測的濕敏電阻器。

即使采用相同的材料,由于要求的提高也可能需要采用新的沉積方法。

總而言之,隨著技術節點的推進,對電介質薄膜沉積的材料和工藝都提出了更高的要求,新的材料和工藝將不斷涌現。

深圳市慈安科技有限公司http://cakj.51dzw.com

在后端的互連方面,主要的挑戰來自RC延遲,為了降低RC延遲,電介質h值必須隨著技術節點不斷降低。

從180/130nm采用摻氟的氧化硅(FSG)到90/65/40nm采用致密摻碳的氧化硅(SiCOH),再到32nm以后的多孔的摻碳氧化硅(p SiCOH),材料的h值從3,5到3.0~2.7,再到小于2.5。

不僅金屬間電介質,在銅化學機械拋光后的表面沉積介質阻擋層的乃值也必須不斷降低。

后端的多孔摻碳氧化硅的沉積,在常規的等離子體增強CVD(PECVD)沉積過程中,需要加人造孔劑,然后通過紫外固化的方法除去造孔劑,從而在薄膜內留下納米尺寸的孔隙。

電路環境中檢測氣敏電阻器的方法,根據實測結果可對氣敏電阻器的好壞作出判斷:

將氣敏電阻器放置在電路中,氣敏電阻器檢測到氣體濃度發生變化時所在電路申的電壓參數也應發生變化,否則,多為氣敏電阻器損壞。

在正常情況下,光敏電阻器應有一個固定阻值,所在環境光線變化時,阻值隨之變化,否則多為光敏電阻器異常。

濕敏電阻器的檢測方法與熱敏電阻器的檢測方法相似,不同的是在測過改變濕度條件,用萬用表檢測濕敏電阻器的阻值變化情況判斷好壞,為電路中待測的濕敏電阻器。

即使采用相同的材料,由于要求的提高也可能需要采用新的沉積方法。

總而言之,隨著技術節點的推進,對電介質薄膜沉積的材料和工藝都提出了更高的要求,新的材料和工藝將不斷涌現。

深圳市慈安科技有限公司http://cakj.51dzw.com

公網安備44030402000607

公網安備44030402000607