用于混合信號和RF集成電路的ESD結構

發布時間:2012/4/22 16:50:52 訪問次數:728

在混合信號和RF應用領域,ESD保護HL2606電路的設計更具有挑戰性。對于混合信號集成電路來說,由于在芯片上的不同電路模塊通常具有不同的性能,而且通常使用不同的電源電壓,從1. 8V到50V甚至高。設計師需要選擇不同的ESD結構,以優化整個芯片的ESD性能。在絕大多數情況下,普適的ESD保護結構并不存在。在RF和VDSM lC ESD保護設計中的主要挑戰來自于ESD網絡和核心IC電路保護的本身的相互影響。ESD設計時首先要求芯片尺寸小,再次就是ESD誘導的寄生效應(即RC延遲和噪聲)盡可能小。需要注意的是,對于不同的工藝,ESD并不是通用的,即使采用同一種工藝,不同的產品系列所采用的結構也是不同的。成功的ESD設計,需要采用定制的手段,采用具體的優化。

在混合信號和RF應用領域,ESD保護HL2606電路的設計更具有挑戰性。對于混合信號集成電路來說,由于在芯片上的不同電路模塊通常具有不同的性能,而且通常使用不同的電源電壓,從1. 8V到50V甚至高。設計師需要選擇不同的ESD結構,以優化整個芯片的ESD性能。在絕大多數情況下,普適的ESD保護結構并不存在。在RF和VDSM lC ESD保護設計中的主要挑戰來自于ESD網絡和核心IC電路保護的本身的相互影響。ESD設計時首先要求芯片尺寸小,再次就是ESD誘導的寄生效應(即RC延遲和噪聲)盡可能小。需要注意的是,對于不同的工藝,ESD并不是通用的,即使采用同一種工藝,不同的產品系列所采用的結構也是不同的。成功的ESD設計,需要采用定制的手段,采用具體的優化。

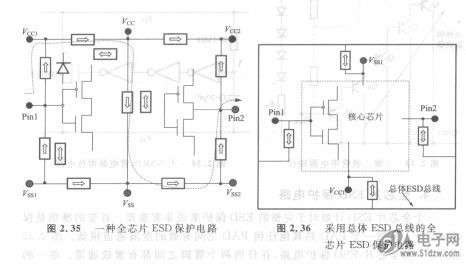

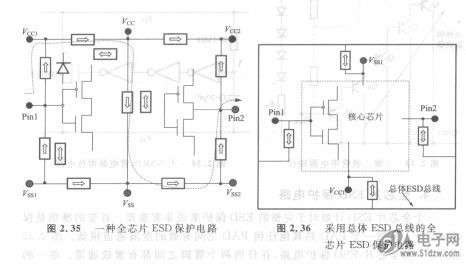

上一篇:全芯片ESD保護電路

上一篇:模擬管腳的ESD保護設計

公網安備44030402000607

公網安備44030402000607