四位數比較器

發布時間:2012/12/8 19:47:06 訪問次數:2069

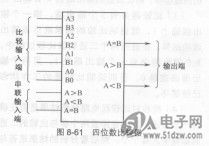

圖8-61所示是四位數EPF10K100GC503-3比較器(集成電路四位數比較器)。電路中,左側上面一排共8個輸入端,分別是兩個數A和B的四位輸入端。左側下面一排共3個串聯輸入端,如果只是用作四位數比較器時,這3個串聯輸入端不起作用,如果要用這種電路進行更多位數的比較時,這3個串聯輸入端將另一個多位比較器電路相串聯,從而可構成大于四位數的比較器電路。電路的右側是3個輸出端,與一位數比較器電路的3個輸出端作用相同。

關于比較器電路主要說明下列幾點。

(1) -位數比較器是最基本的比較器電路,多位數比較器是實用的比較器電路。注意,一位數比較器只有兩個輸入端A和B,但有3個輸出端A=B、A>B和A<B。

(2)多位數比較器的工作原理是從最高位向下一位進行比較,若有結果就會使A>B或A<B輸出端輸出1,若比較到最后一位數時仍然是相等,則比較器的輸出端A=B輸出1。

(3)比較器共有3個輸出端,哪一個輸出端輸出1,就說明比較的結果就是該輸出端的結果。在進行兩個二進制數比較過程中,3個輸出端必有一個輸出端是1,另兩個輸出端必定是0,否則說明比較器的工作狀態已被破壞。

(4)檢驗對比較器電路分析結果是否正確有一個方法,就是直接看兩個參與比較的二進制數哪個大哪個小,然后看分桁的結果是否與直接比較的結果一致。例如,A數是1101,B數是1001,這兩個數中A數是大于B數的,比較器電路分析的結果應該是A>B端輸出l,否則就是電路分析錯誤。

圖8-61所示是四位數EPF10K100GC503-3比較器(集成電路四位數比較器)。電路中,左側上面一排共8個輸入端,分別是兩個數A和B的四位輸入端。左側下面一排共3個串聯輸入端,如果只是用作四位數比較器時,這3個串聯輸入端不起作用,如果要用這種電路進行更多位數的比較時,這3個串聯輸入端將另一個多位比較器電路相串聯,從而可構成大于四位數的比較器電路。電路的右側是3個輸出端,與一位數比較器電路的3個輸出端作用相同。

關于比較器電路主要說明下列幾點。

(1) -位數比較器是最基本的比較器電路,多位數比較器是實用的比較器電路。注意,一位數比較器只有兩個輸入端A和B,但有3個輸出端A=B、A>B和A<B。

(2)多位數比較器的工作原理是從最高位向下一位進行比較,若有結果就會使A>B或A<B輸出端輸出1,若比較到最后一位數時仍然是相等,則比較器的輸出端A=B輸出1。

(3)比較器共有3個輸出端,哪一個輸出端輸出1,就說明比較的結果就是該輸出端的結果。在進行兩個二進制數比較過程中,3個輸出端必有一個輸出端是1,另兩個輸出端必定是0,否則說明比較器的工作狀態已被破壞。

(4)檢驗對比較器電路分析結果是否正確有一個方法,就是直接看兩個參與比較的二進制數哪個大哪個小,然后看分桁的結果是否與直接比較的結果一致。例如,A數是1101,B數是1001,這兩個數中A數是大于B數的,比較器電路分析的結果應該是A>B端輸出l,否則就是電路分析錯誤。

公網安備44030402000607

公網安備44030402000607