基集成電路的工作原理

發布時間:2013/2/18 17:49:26 訪問次數:1003

要點提示

時基集成電路將模擬電路與數字電VIPer12A路巧妙地結合在一起,從而可實現多種用途。

時基集成電路工作原理是:當置“o”端≥÷%。時,輸出端為"0",放電端導通;當置"1"端≤÷Ve。時,輸出端為"1",放電端截止:當復位端為“O”時,輸出端恒為“0”。

時基集成電路的結構特點

時基集成電路的特點

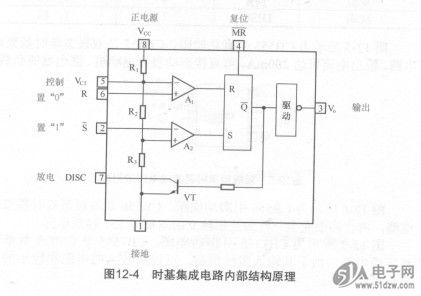

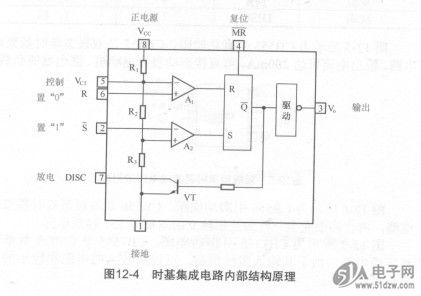

時基集成電路將模擬電路與數字電路巧妙地結合在一起,從而可實現多種用途。圖12-4所示為時基集成電路內部電路方框圖。電阻R.、R2. R3組成分壓網絡,為Ai、A2兩個電壓比較器提供詈Vcc和}‰的基準電壓。兩個比較器的輸出分別作為RS觸發器的置“0”信號和置“1”信號。輸出驅動級和放電管VT受RS觸發器控制。

要點提示

時基集成電路將模擬電路與數字電VIPer12A路巧妙地結合在一起,從而可實現多種用途。

時基集成電路工作原理是:當置“o”端≥÷%。時,輸出端為"0",放電端導通;當置"1"端≤÷Ve。時,輸出端為"1",放電端截止:當復位端為“O”時,輸出端恒為“0”。

時基集成電路的結構特點

時基集成電路的特點

時基集成電路將模擬電路與數字電路巧妙地結合在一起,從而可實現多種用途。圖12-4所示為時基集成電路內部電路方框圖。電阻R.、R2. R3組成分壓網絡,為Ai、A2兩個電壓比較器提供詈Vcc和}‰的基準電壓。兩個比較器的輸出分別作為RS觸發器的置“0”信號和置“1”信號。輸出驅動級和放電管VT受RS觸發器控制。

上一篇:時基集成電路的符號

上一篇:時基集成電路的引腳功能

公網安備44030402000607

公網安備44030402000607