部分譯碼法

發布時間:2014/6/3 20:48:34 訪問次數:6404

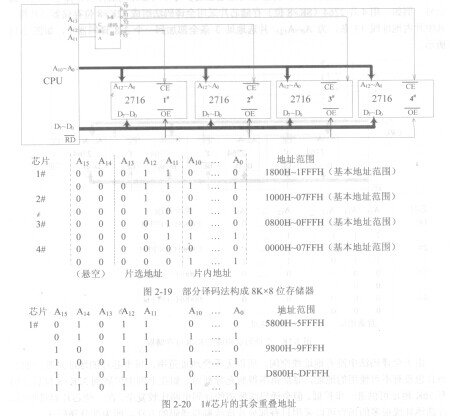

部分譯碼法是指用CPU的部分高位地址線參與譯碼后作為存儲芯片的片選信號。它是SN74HC165DR線選法寫全譯碼法的一個折中,一方面可以簡化譯碼器的設計,另一方面有較強的存儲器容量擴展能力和連續的存儲器范圍。例如,用4片2716擴展存儲器的容量,如圖2-19所示。

圖2-19中采用3條高位地址線A13~All加到一個3-8譯碼器的輸入端,選用其中的4條輸出作為4塊芯片的片選信號。此時,為了確定每片芯片的地址范圍,懸空沒用到的高位地址( Ais、A14)可假設為“0”,這樣確定出來的地址與線選法中的一樣,都稱為“基

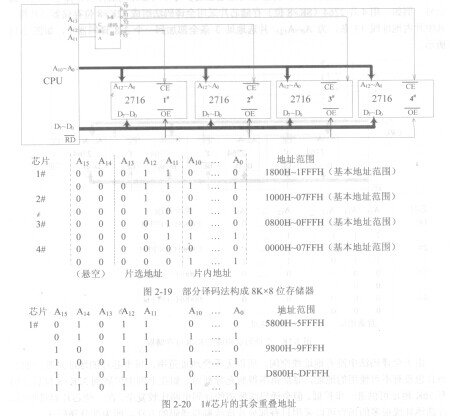

本地址”,確定的方法不變。同樣,部分譯碼法也存在重疊地址,而且重疊地址的個數m與懸空地址線的條數n的關系為:m=2“,在本例中每片芯片共有4個重疊地址(其中一個為基本地址),分別假設當A15A14=01、10和11時,其余的地址確定方法不變。例如,14芯片的其余重疊地址如圖2-20所示。

圖2-20 芯片的其余重疊地址

用同樣的方法,不難寫出其余芯片的重疊地址。部分譯碼法的連接方案中,由于地址重疊,影響了地址區的有效使用,也限制了存儲器的擴展。因此,在選用部分譯碼時,也要盡可能多選一些高位地址線來作為譯碼器的輸入。

部分譯碼法是指用CPU的部分高位地址線參與譯碼后作為存儲芯片的片選信號。它是SN74HC165DR線選法寫全譯碼法的一個折中,一方面可以簡化譯碼器的設計,另一方面有較強的存儲器容量擴展能力和連續的存儲器范圍。例如,用4片2716擴展存儲器的容量,如圖2-19所示。

圖2-19中采用3條高位地址線A13~All加到一個3-8譯碼器的輸入端,選用其中的4條輸出作為4塊芯片的片選信號。此時,為了確定每片芯片的地址范圍,懸空沒用到的高位地址( Ais、A14)可假設為“0”,這樣確定出來的地址與線選法中的一樣,都稱為“基

本地址”,確定的方法不變。同樣,部分譯碼法也存在重疊地址,而且重疊地址的個數m與懸空地址線的條數n的關系為:m=2“,在本例中每片芯片共有4個重疊地址(其中一個為基本地址),分別假設當A15A14=01、10和11時,其余的地址確定方法不變。例如,14芯片的其余重疊地址如圖2-20所示。

圖2-20 芯片的其余重疊地址

用同樣的方法,不難寫出其余芯片的重疊地址。部分譯碼法的連接方案中,由于地址重疊,影響了地址區的有效使用,也限制了存儲器的擴展。因此,在選用部分譯碼時,也要盡可能多選一些高位地址線來作為譯碼器的輸入。

上一篇:全譯碼法

上一篇:存儲器字數和位數的擴展

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607