深圳市哲瀚電子科技專業代理芯聯系列產品:CL1221 CL1226 CL6807 CL6807 CL1570KSD CL1570ESD CL1570EDD CL1570ESK CL1570EDK CL5184OP CL5183OP等更多型號,歡迎咨詢0755-83224649陳小姐QQ3012323310

CL6807是一款高側電流感應的高亮度LED驅動控制器,設計運用于高效驅動由高于LED正向導通電壓的電源供電的單個或多個串聯LED。該裝置的運作是在6V到35V之間,提供了一個外部可調的高達1A的輸出電流。根據電力供應的電壓和外部元件,可以提供高達25瓦的輸出功率。

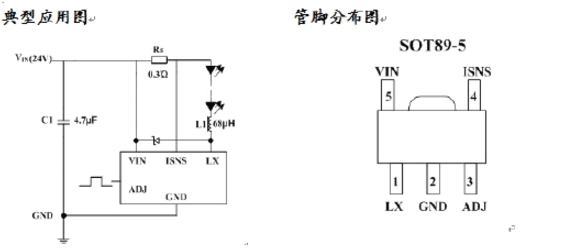

CL6807包括輸出開關和一個高側的輸出電流傳感電路, 可利用外部電阻器來設定的平均輸出電流或由精心設計的直流電壓或PWM信號來加載ADJ腳來調節輸出電流。在ADJ腳上加低于0.5V的電壓將關斷輸出電流和開關動作,使該芯片進入低功耗待機狀態。CL6807的封裝為SOT89-5。

特點:

◆ 極少的外圍器件數

◆ 寬輸入電壓范圍:6V至35V

◆ 高達1A的輸出電流

◆ 開關控制及亮度的直流電壓控制和PWM控制由單腳實現

◆ 輸出電流準確性可達±5%

◆ 內建的LED開路保護

◆高達95%的效率

◆高測電流感應

◆遲滯控制,無需補償

應用:

◆LED替換低壓鹵素燈應用

◆汽車照明

◆ 低壓照明工業

◆ LED后備照明

◆ 發亮標志

◆ 緊急照明系統

◆ 液晶電視背光

有人說,摩爾定律不再重要了,并認為它純粹是一個技術問題,或者只是幾家巨頭間的競賽。還有人說,除了某幾個特定領域,遵循摩爾定律已讓成本太過高昂。更有人說,摩爾定律已死。真相究竟是什么?

“其中大部分觀點是錯誤的。”英特爾高級院士Mark Bohr此前在一場美國的“制造大會”上表達了自己對摩爾定律的最新看法。他認為,在當今世界僅有幾家公司有能力實現摩爾定律的效益,摩爾定律帶來的不是一場競賽,但一些公司卻背離了摩爾定律的法則,直接的結果就是導致制程節點名稱根本無法正確體現制程位于摩爾定律曲線的哪個位置。

Mark Bohr認為,摩爾定律在任何可預見的未來都不會終結,有一天可能會達到物理極限,但目前還看不到終點。就像1990年,當晶圓上的晶體管大小達到用以印刷它們的光的波長(193納米)時,物理學界明確指出不能再向前推進了,但英特爾突破了那個挑戰。Mark Bohr說,英特爾使用掩模圖形產生的干涉光柵進行印刷,開發了計算型光刻技術和多重曝光。

“每一次英特爾都能在關鍵技術上實現突破,延續摩爾定律。”英特爾內部人士第一財經記者說。

但可以看到,全球晶圓代工已展開新一輪熱戰,無論是臺灣半導體巨擘臺積電還是三星都對英特爾在半導體的龍頭位置虎視眈眈,而臺積電此前甚至表示7納米已于2017年進入風險性試產,三星則表示2018年推出7納米。

“被失效”的摩爾定律

摩爾定律可以說是整個計算機行業最重要的定律,它其實是一個預言:是指每代制程技術都要讓芯片上的晶體管數量翻一番,這意味著芯片的處理能力也加倍,而每代制程工藝在英特爾官方看來是兩年時間。這種指數級的增長,促使上世紀70年代的大型家庭計算機轉化成80、90年代更先進的機器,然后又孕育出了高速度的互聯網、智能手機和現在的車聯網、智能冰箱和自動調溫器等。

而從行業角度來看,業界一直遵循這一定律,并按前一代制程的0.7倍對新制程節點命名,這種線性升級正好帶來晶體管集成密度翻番。因此,出現了90納米、65納米、45納米、32納米——每一代制程節點都能在給定面積上,容納比前一代多一倍的晶體管。

但隨著技術的發展,由于同樣小的空間里集成越來越多的硅電路,產生的熱量也越來越大,這種原本兩年處理能力加倍的速度在很多人看來已經慢慢下滑,這是摩爾定律質疑聲中最大的“噪音”。

比如英偉達認為,CPU晶體管和能量大幅上升導致應用性能只有小幅增長,Dennard(登納德)縮放效應遇到了元件物理的瓶頸。

“但是事實上,隨著制程技術演進、晶體管密度提高,英特爾預計單個晶體管的成本將持續下降,而且針對7納米、5納米以及更小的制程,英特爾有著強大的研發渠道和規劃。”英特爾內部人士對第一財經記者表示,此前摩爾定律已經“被失效”了很多次,但每一次英特爾都能在關鍵技術上實現突破,延續摩爾定律。

Mark Bohr在上述大會中還提到了一個觀點:摩爾定律不會因為無用而結束,它的進步也不會因為經濟效益不足而受阻,并且,在物理學方面,摩爾定律也不會遇到瓶頸。

“誠然,有一天我們可能會達到物理極限,但目前還看不到終點。這得益于我們持續的創新,比如目前在14納米制程中使用的鰭式場效應晶體管(FinFET)和超微縮技術(hyper scaling),升級版的超微縮技術已應用在我們即將量產的10納米制程,而得益于這一新的工藝突破,我們可以維持每百萬晶體管的成本不變。”Mark Bohr認為,英特爾通過發現挑戰所在,各個擊破解決問題,不斷突破各種障礙,而目前英特爾已經已著眼7納米和5納米制程的研發。

三星和臺積電實現制程反超?

經過大規模整合,半導體行業中有能力制造最先進芯片的公司已從10年前的十幾家變為如今屈指可數的幾家。除了英特爾,目前這份名單上只剩下三星、臺積電和2009年從AMD拆分出來的格羅方德。

據記者了解,以主流先進制程競爭來說,2017年上半年臺積電10納米已經開始放量增長,并且7納米已于2017年進入風險性試產。據中國臺灣媒體報道,臺積電5納米則會在2019年進入風險試產階段,2020年正式量產。與此同時,三星電子也在追趕,除了2017年8納米LPP制程進入風險試產外,2018年將推出7納米,同時,三星也表示2019年將推出5、6納米制程,2020年投產4納米并導入環繞式閘極架構。

AMD今年推出的Ryzen處理器更是使用了由格羅方德提供的的14nm LPP(Low Power Plus低功耗加強版)工藝,簡單來說,英特爾的競爭對手們都在發力追趕。

手機聯盟秘書長王艷輝對記者表示,對手的“激進”導致了英特爾的被動,特別是在“制程數字”的比較中。因為直到前不久,才聽到了英特爾發布首批10納米制程、第8代Core i移動版U系列處理器的消息。

但在英特爾看來,英特爾依然是技術的領先者,以10納米為例,制程的晶體管密度是業界其他10納米制程的約2倍。

“也許是因為進一步的制程升級越來越難,一些公司背離了摩爾定律的法則。即使晶體管密度增加很少,或者根本沒有增加,但他們仍繼續推進采用新一代制程節點命名。結果導致制程節點名稱根本無法正確體現這個制程位于摩爾定律曲線的哪個位置。”Mark Bohr說。

他甚至還給出了一個衡量半導體工藝水平的公式。簡單來說,公式分為兩部分,一部分計算2bit NAND(4個晶體管)的密度,另一部分是用來計算的是SFF(scan flip flop)的晶體管密度,0.6和0.4兩個數字是這兩部分的加權系數。Bohr指出衡量半導體工藝真正需要的是晶體管密度。

與此同時,Mark Bohr希望其他半導體廠商在關于自家工藝節點介紹的時候也應該公布邏輯芯片的晶體管密度,以及SRAM cell的單元面積。

“說白了英特爾希望競爭對手們都把參數底牌亮出來,但三星和臺積電顯然不會這么做。”王艷輝對記者說,目前來看,制程工藝確實不能只看納米的數據,拋去技術參數,誰能依靠技術奪得更多的客戶才是當前最重要的問題。

公司:深圳市哲瀚電子科技有限公司

聯系人:陳小姐

手機:13714441972

電話:0755-82549527/83259945/13714441972

傳真:0755-83259945

地址:深圳市福田區深圳市福田區華強北街道深南中路3006號佳和大廈3C006