可編程邏輯(PLD)是由一種通用的集成電路產生的,邏輯功能按照用戶對器件編程來確定,用戶可以自行編程把數字系統集成在PLD中。經過多年的發展,可編程邏輯器件由70年代的可編程邏輯陣列器件 (PLD) 發展到目前的擁有數千萬門的現場可編程陣列邏輯 (FPGA),隨著人工智能研究的火熱發展,FPGA的并行性已經在一些實時性很高的神經網絡計算任務中得到應用。由于在FPGA上實現浮點數會耗費很多硬件資源,而定點數雖然精度有限,但是對于不同應用通過選擇合適的字長精度仍可以保證收斂,且速度要比浮點數表示更快而且資源耗費更少,已經使其成為嵌入式AI和機器學習應用程序的理想選擇。

最新的證明點是英國伯明翰大學電子電氣和系統工程系的Yufeng Hao和Steven Quigley最近發表的論文。論文標題為“在Xilinx FPGA上實現深度遞歸神經網絡語言模型“,介紹了使用Python編程語言成功實現和訓練基于固定點深度遞歸神經網絡(DRNN); Theano數學庫和多維數組的框架; 開源的基于Python的PYNQ開發環境; Digilent PYNQ-Z1開發板以及PYNQ-Z1板上的賽靈思Zynq Z-7020的片上系統SoC。Zynq-7000系列裝載了雙核ARM Cortex-A9處理器和28nm的Artix-7或Kintex-7可編程邏輯。在單片上集成了CPU,DSP以及ASSP,具備了關鍵分析和硬件加速能力以及混合信號功能,出色的性價比和最大的設計靈活性也是特點之一。使用Python DRNN硬件加速覆蓋(一種賽靈思公司提出的硬件庫,使用Python API在硬件邏輯和軟件中建立連接并交換數據),兩個合作者使用此設計為NLP(自然語言處理)應用程序實現了20GOPS(10億次每秒)的處理吞吐量,優于早期基于FPGA的實現2.75倍到70.5倍。

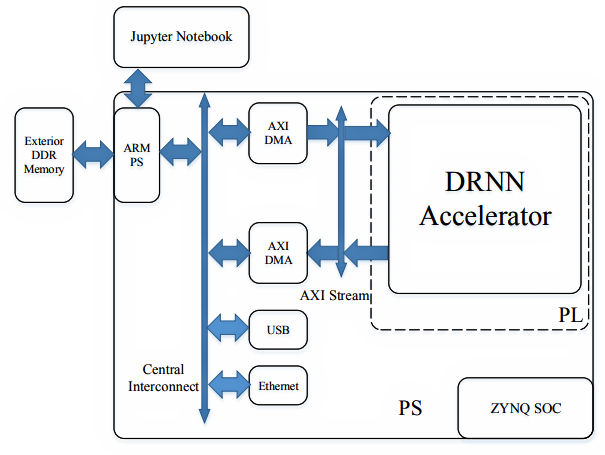

論文的大部分討論了NLP和LM(語言模型),“它涉及機器翻譯,語音搜索,語音標記和語音識別”。本文隨后討論了使用VivadoHLS開發工具和Verilog語言實現DRNN LM硬件加速器,可以為PYNQ開發環境合成一個定制的硬件覆蓋。由此產生的加速器包含五個過程元素(PE),能夠在此應用程序中提供20GOPS的數據吞吐量。以下是設計的框圖:

DRNN加速器框圖

Vivado設計套件為下一代超高效率的C/C++和基于IP的設計提供了新的方法。融入了新的超快高效率設計方法集,用戶可以實現10-15倍的效率的提升。Vivado HLS支持ISE和Vivado設計環境,可以通過集成C,C++和SystemC標準到賽靈思的可編程器件中而無需創建RTL模型,加快IP的創建。

這篇論文中包括了大量深入的技術細節,但是這一句話總結了這篇博客文章的理由:“更重要的是,我們展示了軟件和硬件聯合設計和仿真過程在神經網絡領域的應用“。考慮到PYNQ-Z1開發板的售價為229美元,這種說法是完全正確的。

以下有貨,歡迎咨詢

XC6SLX45-3CSG324I

XC6SLX100-2FGG676C

XC6SLX4-2TQG144C

XC7Z030-1FBG484C

XC7VX1140T-2FLG1926I

XC7K355T-1FFG901C

XQ5VSX50T-1EF665I

XQ5VSX50T-2EF665I

XQ5VSX95T-1EF1136I

SG2823L/883B

SG2803L/883B

5SGSMD5K2F40C3N

XCVU9P-1FLGA2104C

XCVU5P-1FLVB2104E

聲明:本文來源于XilinxXcell Daily Blog,由創新網賽靈思中文社區編譯,轉載請注明作者、出處及原文鏈接