Vivado系統生成器工具能方便地接入平臺設計,從而可充分利用開發板接口和處理系統。

FPGA的應用不斷拓展,同時FPGA設計流程也隨之不斷演進。我們不再將FPGA用作簡單的膠合邏輯,甚至不再作為信號處理鏈的核心,用以將IP與專有后端接口集成。相反,FPGA正在轉變為可編程片上系統,其中包含作為處理器外設的硬件以及在強大APU上運行的高級軟件。這種架構就是我們所說的賽靈思全可編程SoC。

為了充分發揮這種全新流程的優勢,我們需要將設計方法從FPGA早期的自上而下RTL轉變為以IP開發和標準化連接(例如ARM®的高級可擴展接口 (AXI))為中心的自下而上流程。隨著接口從定制接口發展為通用接口,我們就可以花更少的精力來驗證數據路徑與平臺設計之間的交互。

賽靈思DSP系統生成器(System Generator for DSP)同樣也得到了發展。該工具是Vivado®設計套件的一部分,其通過將DSP數據路徑整合到用Vivado IP Integrator工具構建的平臺設計中,打造出全新的自下而上設計方法。我們仔細看看系統生成器(System Generator)實現的設計自動化如何幫助高性能設計充分利用平臺連接功能。

構建全可編程平臺框架

通過定義用來存放數據路徑的平臺框架,我們可以啟動全新的設計流程。Vivado工具套件能識別開發板;我們將利用開發板自動化功能構建新的平臺設計。

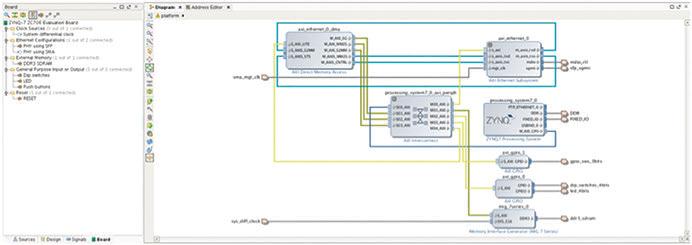

如圖1所示,平臺設計或平臺框架的基本組成包括:處理器級和開發板級接口,以及將其組合在一起的邏輯。我們將平臺框架作為系統級設計的基礎(即外殼),這給我們的數據路徑提供了空間。模塊和連接功能自動化通過IP外設將處理系統連接到板級接口。封裝在IP Catalog中的DSP數據路徑或軟件加速器利用賽靈思Designer Assistance自動化功能方便地連接到我們的處理器平臺框架中,進而連接到外部器件接口。

圖1 –將處理系統連接到板級接口的平臺框架實例

創建作為可輸入IP的數據路徑

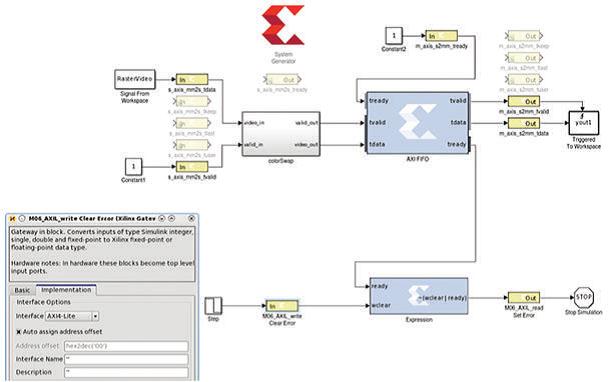

我們的最終目標是讓數據路徑能進入全可編程平臺框架。如果要從頭開始,我們可以用標準化接口創建數據路徑。如圖2所示,只需將網關端口迅速標記為AXI4-Lite接口,或者對端口進行命名以匹配標準連接(如Simulink®圖上的AXI4-Stream),這樣,System Generator為Vivado IP Catalog打包設計時就會為設計添加額外邏輯并將通用信號收集到接口內。

圖2 – 自動將網關導入AXI4-Lite和AXI4-Stream接口

不過,我們利用一種新設計方法,使用平臺框架定制一個可集成到全可編程設計的插件。我們使用自動化功能確定平臺設計中現有哪些接口,哪些接口與開發板關聯,以及哪些接口可為DSP數據路徑創建插件。既然我們的目標是將數據路徑轉換為可連接至平臺框架的IP,因此我們不需要關注板級接口,而是關注標準化AXI接口。開發板上的每個不關聯接口轉變為System Generator網關。這些網關在System Generator中充當簡單信號,當我們將平臺設計導出到IP Catalog時,這些網關會生成用以連接平臺設計的AXI 接口。

如實例所示,AXI4-Lite接口創建獨立的讀/寫信號,在導出到Vivado工具套件時共享通用的可尋址寄存器接口。簡單的復制-粘貼使我們在地址偏移位置通過相同接口獲得更多用于處理器的直接寄存器。同時,我們可自動生成軟件驅動API以讀/寫寄存器。

如果平臺設計中提供AXI4-Stream接口,System Generator會向模型添加正確匹配的網關。AXI4- Stream接口極其靈活并包含很多信號。ACLK時鐘源與該接口相關聯,但該信號直接作為這部分數據路徑的抽象系統時鐘。TVALID信號表示接口有效。其他信號為可選信號。System Generator會將初始流接口中的信號添加到我們的模型,不過我們可以通過刪除或添加信號來滿足內部要求。

在圖2所示的模型中,我們的數據路徑只關心TDATA(經接口發送的數據)和S_AXIS接口上的TVALID。為刪除不必要的信號,我們針對該模型對沒用的網關添加注釋,因為默認值將會驅動IP Integrator中的信號連接。

AXI4-Lite和AXI4-Stream信號能利用自下而上方法輕松進行仿真和驗證。AXI4-Lite接口建模為用于訪問大量Simulink模塊的簡單網關,實現網關一側到另一側數據傳送的抽象。同樣,AXI4-Stream接口只是一系列遵循簡單握手規則的信號,以將數據從一個IP核傳遞到另一個。

仿真建模的唯一挑戰在于接口上所用的可選端口。如果我們每個周期都接收數據并通過數據路徑無中斷地進行處理,我們就不需要TREADY握手信號。簡化模型通過TDATA 網關將矢量的每個元素從Simulink的信號發送到Workspace令牌。當需要完整握手時,我們用AXI4-Stream FIFO進行建模以緩沖數據,如圖2中的M_AXIS接口所示。

這種定制的自動化功能可作為創建連接平臺框架的IP的起點。不過,System Generator很靈活,允許我們添加或刪除部分甚至整個AXI接口。最終可將數據路徑轉換為可在多個系統級設計中重用的IP。

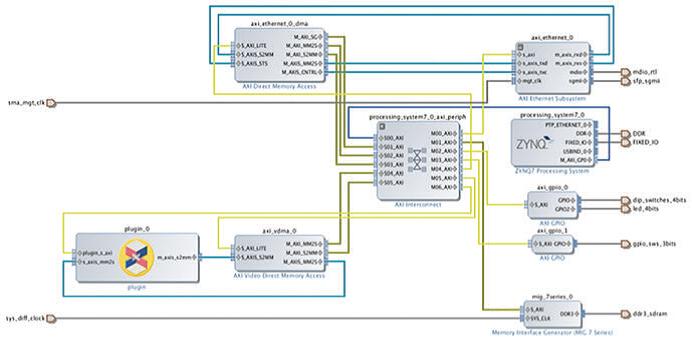

添加邏輯后,最后一步是將使用DSP系統生成器構建的數據路徑導出到Vivado IP Catalog。這種操作能實現接口的簡單連接,無論使用RTL還是在IP Integrator中都是如此。此外,我們還生成在SDK中使用的驅動器,并將具有最佳測試向量數據的仿真模型連接到IP。由于我們在創建DSP數據路徑時事先知道平臺框架的情況,因此能自動組合模型和平臺設計,如圖3中的完整系統所示。

圖3 – 將DSP數據路徑連接到平臺框架的平臺系統

降低仿真風險

生成包含硬件加速器、DSP數據路徑或定制邏輯的完整片上系統很具有挑戰性。采用自下而上方式進行仿真以確定數據路徑按預期工作,這種方法風險很大,而且維持可支持數據路徑的平臺接口帶寬同樣很困難。

我們通過使用標準化接口開發能降低仿真風險的IP。這是因為接口級的交互被抽象化,使我們專注于驗證內部數據路徑。最后,通過利用開發板、模塊和連接的智能自動化功能,我們可生成基于平臺的系統,從而滿足我們的需求并集成自定義數據路徑。

XC7VX690T-2FFG1926E

XC7VX690T-3FFG1157E

XC7VX690T-L1FF1926E

XC7VX690T-2FFG1157C

XC7VX485T-1FF1157C

XC7VX415T-2FF1157C

XC7VX690T-1FF1157C

XC7VX485T-2FF1157C

XC7VX690T-1FFG1157C

XC7VX485T-1FFG1157C

XC7VX330T-3FFG1157C

EP2S130F1020I5N

EP2S130F1020C4N

EP2S130F1020C3N