FI-RE31S-HF 非阻塞型賦值

發布時間:2019/10/16 21:37:01 訪問次數:3214

FI-RE31S-HF在always語句中對電平敏感事件和邊沿敏感事件的描述有何不同?

阻塞型賦值和非阻塞型賦值有何區別?

試用verilog描述一個基本sR鎖存器和一個下降沿觸發的SR觸發器。

鎖存器和觸發器都是具有存儲功能的邏輯電路,是構成時序電路的基本邏輯單元。每個鎖存器或觸發器都能存儲1位二值信息,所以又稱為存儲單元或記憶單元.

鎖存器是對脈沖電平敏感的電路,它們在一定電平作用下改變狀態。基本sR鎖存器由輸入信號電平直接控制其狀態,傳輸門控或邏輯門控鎖存器在使能電平作用下由輸入信號決定其狀態。在使能信號作用期間,門控鎖存器輸出跟隨輸入信號變化而變化。

觸發器是對時鐘脈沖邊沿敏感的屯路,根據不同的電路結構,它們在時鐘脈沖的上升沿或下降沿作用下改變狀態。目前流行的觸發器電路主要有主從、維持阻塞和利用傳輸延遲等幾種結構,它們的工作原理各不相同。

觸發器按邏輯功能分類有D觸發器、JK觸發器、T(r′)觸發器和sR觸發器。它們的功能可用特性表、特性方程和狀態圖來描述。觸發器的電路結構與邏輯功能沒有必然聯系。例如JK觸發器既有主從結構的,也有維持阻塞或利用傳輸延遲結構的。每一種邏輯功能的觸發器都可以通過增加門電路和適當的外部連線轉換為其他功能的觸發器。

用verilog對鎖存器與觸發器做行為級描述,是描述時序電路的基礎模塊。

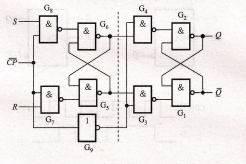

分析圖例5.2.1所示電路的功能,列出功能表.

用cmos電路74HCT02或非構成消除機械開關抖動影響電路如圖題5.2.2所示,試畫出在開關S由位置A到B時Q和Q端的波形.如改用TTL電路74LS02實現,r1,r2取值的大致范圍為多少?整個電路的功耗會發生什么變化.

由與非或非門組成的SR鎖存器如圖題5.2.3所示,試分析其工作原理并列出功能表.

FI-RE31S-HF在always語句中對電平敏感事件和邊沿敏感事件的描述有何不同?

阻塞型賦值和非阻塞型賦值有何區別?

試用verilog描述一個基本sR鎖存器和一個下降沿觸發的SR觸發器。

鎖存器和觸發器都是具有存儲功能的邏輯電路,是構成時序電路的基本邏輯單元。每個鎖存器或觸發器都能存儲1位二值信息,所以又稱為存儲單元或記憶單元.

鎖存器是對脈沖電平敏感的電路,它們在一定電平作用下改變狀態。基本sR鎖存器由輸入信號電平直接控制其狀態,傳輸門控或邏輯門控鎖存器在使能電平作用下由輸入信號決定其狀態。在使能信號作用期間,門控鎖存器輸出跟隨輸入信號變化而變化。

觸發器是對時鐘脈沖邊沿敏感的屯路,根據不同的電路結構,它們在時鐘脈沖的上升沿或下降沿作用下改變狀態。目前流行的觸發器電路主要有主從、維持阻塞和利用傳輸延遲等幾種結構,它們的工作原理各不相同。

觸發器按邏輯功能分類有D觸發器、JK觸發器、T(r′)觸發器和sR觸發器。它們的功能可用特性表、特性方程和狀態圖來描述。觸發器的電路結構與邏輯功能沒有必然聯系。例如JK觸發器既有主從結構的,也有維持阻塞或利用傳輸延遲結構的。每一種邏輯功能的觸發器都可以通過增加門電路和適當的外部連線轉換為其他功能的觸發器。

用verilog對鎖存器與觸發器做行為級描述,是描述時序電路的基礎模塊。

分析圖例5.2.1所示電路的功能,列出功能表.

用cmos電路74HCT02或非構成消除機械開關抖動影響電路如圖題5.2.2所示,試畫出在開關S由位置A到B時Q和Q端的波形.如改用TTL電路74LS02實現,r1,r2取值的大致范圍為多少?整個電路的功耗會發生什么變化.

由與非或非門組成的SR鎖存器如圖題5.2.3所示,試分析其工作原理并列出功能表.

公網安備44030402000607

公網安備44030402000607