BZT52-C5V6ST/R 數字電路中的電子器件

發布時間:2019/10/25 11:41:48 訪問次數:1097

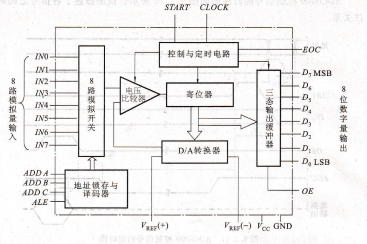

BZT52-C5V6ST/RADC0809內部結構框圖

圖9.2.10中各引腳作用如下:

fⅣ0~flV7:8路模擬信號輸入端。

D7~DO:8位數字信號輸出端。

CLOCK;時鐘信號輸人端。

ADD4、ADDB、ADDC:地址碼輸人端,不同的地址碼選擇不同通道的模擬量輸人。

ALE:地址碼鎖存輸入端,當輸入地址碼穩定后,ALE的上升沿將地址信號鎖存于地址鎖存器內.

vrEF(+)、vref(-):分別為參考電壓的正、負輸入端。一般情況下vrefⅢ(+)接

vcc,vrEF(-)接GND.

smRr:啟動信號輸入端。該信號的上升沿到來時片內寄存器被復位,在其下降沿開始A/D轉換。

EOC:轉換結束信號輸出端。當A/D轉換結束時EaC變為高電平,并將轉換結果送入三態輸出緩沖器,EOC可以作為向CPU發出的中斷請求信號。

0E:輸出允許控制輸入端。當0E=1時,三態輸出緩沖器的數據送到數據總線。

在使用時應注意以下幾點:

轉換時序,電子電路按功能分為模擬電路和數字電路。根據電路的結構特點及其對輸人信號響應規則的不同,數字電路可分為組合邏輯電路和時序邏輯電路。數字電路中的電子器件,例如二極管、三極管(BJT、FET)處于開關狀態,時而導通,時而截止,構成電子開關。這些電子開關是組成邏輯門電路的基本器件。邏輯門電路又是數字電路的基本單元。如果將這些門電路集成在一片半導體芯片上就構成數字集成電路。

數字電路主流形式是數字集成電路。從20世紀60年代開始,數字集成器件以雙

極型工藝制成了小規模邏輯器件,隨后發展到中規模;70年代末,微處理器的出現,使數字集成電路的性能發生了質的飛躍;從80年代中期開始,專用集成電路(ASIC①)制作技術已趨成熟,標志著數字集成電路發展到了新的階段。ASIC是將一個復雜的數字系統制作在一塊半導體芯片上,構成體積小、重量輕、功耗低、速度高、成本低且具有保密性的系統級芯片。ASIC芯片的制作可以采用全定制或半定制的方法。全定制適用于生產批量的成熟產品.

ASIC系Application Spccific lntegrated Circuit的縮寫。

PLD系PrOgrammable Logic Device的縮寫。

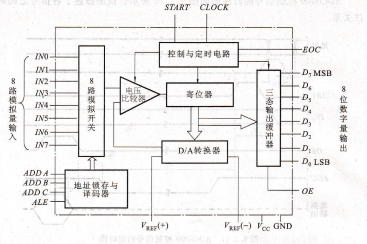

BZT52-C5V6ST/RADC0809內部結構框圖

圖9.2.10中各引腳作用如下:

fⅣ0~flV7:8路模擬信號輸入端。

D7~DO:8位數字信號輸出端。

CLOCK;時鐘信號輸人端。

ADD4、ADDB、ADDC:地址碼輸人端,不同的地址碼選擇不同通道的模擬量輸人。

ALE:地址碼鎖存輸入端,當輸入地址碼穩定后,ALE的上升沿將地址信號鎖存于地址鎖存器內.

vrEF(+)、vref(-):分別為參考電壓的正、負輸入端。一般情況下vrefⅢ(+)接

vcc,vrEF(-)接GND.

smRr:啟動信號輸入端。該信號的上升沿到來時片內寄存器被復位,在其下降沿開始A/D轉換。

EOC:轉換結束信號輸出端。當A/D轉換結束時EaC變為高電平,并將轉換結果送入三態輸出緩沖器,EOC可以作為向CPU發出的中斷請求信號。

0E:輸出允許控制輸入端。當0E=1時,三態輸出緩沖器的數據送到數據總線。

在使用時應注意以下幾點:

轉換時序,電子電路按功能分為模擬電路和數字電路。根據電路的結構特點及其對輸人信號響應規則的不同,數字電路可分為組合邏輯電路和時序邏輯電路。數字電路中的電子器件,例如二極管、三極管(BJT、FET)處于開關狀態,時而導通,時而截止,構成電子開關。這些電子開關是組成邏輯門電路的基本器件。邏輯門電路又是數字電路的基本單元。如果將這些門電路集成在一片半導體芯片上就構成數字集成電路。

數字電路主流形式是數字集成電路。從20世紀60年代開始,數字集成器件以雙

極型工藝制成了小規模邏輯器件,隨后發展到中規模;70年代末,微處理器的出現,使數字集成電路的性能發生了質的飛躍;從80年代中期開始,專用集成電路(ASIC①)制作技術已趨成熟,標志著數字集成電路發展到了新的階段。ASIC是將一個復雜的數字系統制作在一塊半導體芯片上,構成體積小、重量輕、功耗低、速度高、成本低且具有保密性的系統級芯片。ASIC芯片的制作可以采用全定制或半定制的方法。全定制適用于生產批量的成熟產品.

ASIC系Application Spccific lntegrated Circuit的縮寫。

PLD系PrOgrammable Logic Device的縮寫。

公網安備44030402000607

公網安備44030402000607