集成運放芯片窄通帶幅頻好的濾波器

發布時間:2020/11/7 22:53:07 訪問次數:1337

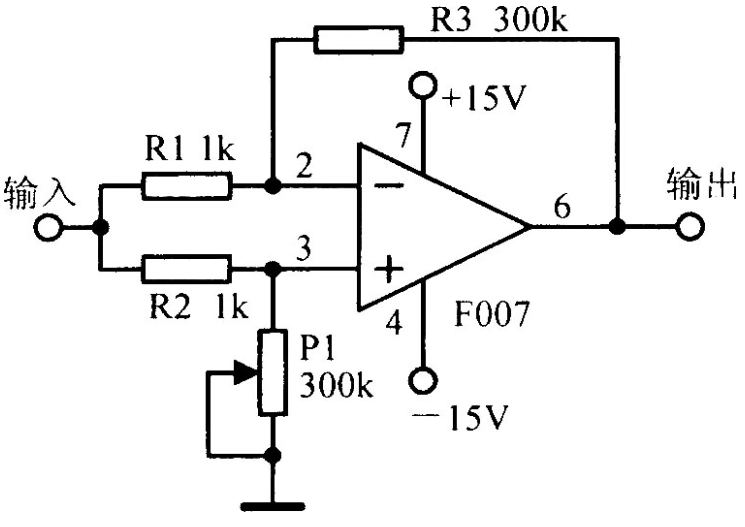

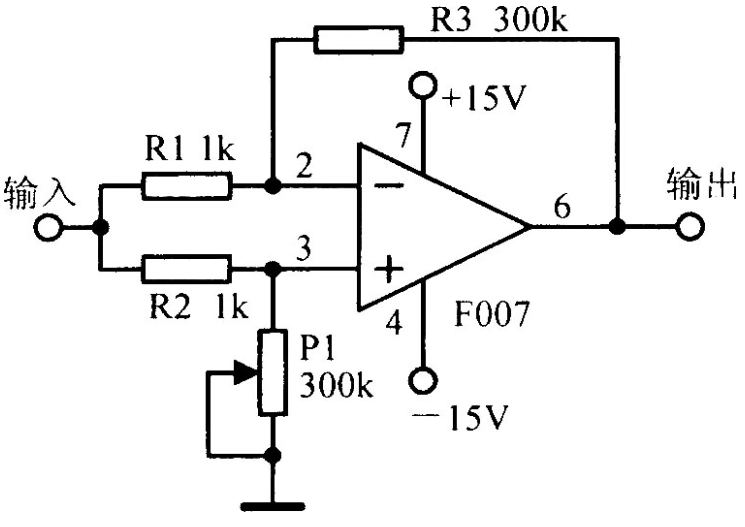

蓄電池Thevinen模型的蓄電池內阻是反映蓄電池狀態的重要參數。目前多頻點內阻測試法是辨識該模型先進有效的技術。Thevene模型中的極化電阻和極化電容對測試信號極為敏感,需要窄通帶幅頻好的濾波器。

采用集成運放芯片LM324N設計帶通濾波單元,只能滿足單一中心頻率帶通濾波,對于不同頻率點,需要重復設計兩個以上濾波電路單元,且由于外圍RC元器件太多,使得一致性很難把握,濾波器的中心增益變化,導致測出的阻值過于波動,進而惡化了儀器的空間布局。

選用有源濾波芯片MAX267,設計可選頻帶的帶通濾波器,極大地縮小了電路空間布局,適合手持便攜式的內阻測試儀的技術要求。

IMG全新的多核技術還可以幫助我們擴展自己的技術能力,以支持未來的處理器設計。

Imagination重要的合作伙伴,他們為汽車、工業和消費類平臺打造了多款行業最典型的系統級芯片(SoC)。相比我們以往提供的所有產品,本次所授權的GPU內核又向前邁出了全新一步。新一代的GPU可以用于德州儀器新一代的SoC之中。

簡單高效的防護單粒子翻轉的電路設計方法。EDAC 主要依據檢錯、糾錯的原理,通過轉換電路將寫入的數據生成校驗碼并保存,當讀出時靠對校驗碼進行判定,若只有一位出錯系統則自動糾正并將正確的數據輸出,同時還會進行數據的回寫從而覆蓋原來出錯的數據。

EDAC盡管糾錯能力強大,但是需要糾錯、譯碼電路,因此結構較為復雜,不適宜用于高性能的數據通道中。EDAC也可用于糾正多bit出錯的情況,但是糾錯電路會更加復雜。

權衡TMR和EDAC的優缺點,通常會在邏輯電路設計中使用TMR,在存儲器讀寫電路中使用EDAC。

CMOS雙二階開關電容有源濾波器芯片,應用廣泛。其內部電路結構如示。芯片內部包含兩個獨立且性能相同的二階濾波單元,可通過外圍匹配的電阻電容構成級聯反饋網絡,設計4階、6階、8階甚至更高階的多級反饋帶通濾波器,可實現切比雪夫、巴特沃斯、貝塞爾、橢圓等類型。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

蓄電池Thevinen模型的蓄電池內阻是反映蓄電池狀態的重要參數。目前多頻點內阻測試法是辨識該模型先進有效的技術。Thevene模型中的極化電阻和極化電容對測試信號極為敏感,需要窄通帶幅頻好的濾波器。

采用集成運放芯片LM324N設計帶通濾波單元,只能滿足單一中心頻率帶通濾波,對于不同頻率點,需要重復設計兩個以上濾波電路單元,且由于外圍RC元器件太多,使得一致性很難把握,濾波器的中心增益變化,導致測出的阻值過于波動,進而惡化了儀器的空間布局。

選用有源濾波芯片MAX267,設計可選頻帶的帶通濾波器,極大地縮小了電路空間布局,適合手持便攜式的內阻測試儀的技術要求。

IMG全新的多核技術還可以幫助我們擴展自己的技術能力,以支持未來的處理器設計。

Imagination重要的合作伙伴,他們為汽車、工業和消費類平臺打造了多款行業最典型的系統級芯片(SoC)。相比我們以往提供的所有產品,本次所授權的GPU內核又向前邁出了全新一步。新一代的GPU可以用于德州儀器新一代的SoC之中。

簡單高效的防護單粒子翻轉的電路設計方法。EDAC 主要依據檢錯、糾錯的原理,通過轉換電路將寫入的數據生成校驗碼并保存,當讀出時靠對校驗碼進行判定,若只有一位出錯系統則自動糾正并將正確的數據輸出,同時還會進行數據的回寫從而覆蓋原來出錯的數據。

EDAC盡管糾錯能力強大,但是需要糾錯、譯碼電路,因此結構較為復雜,不適宜用于高性能的數據通道中。EDAC也可用于糾正多bit出錯的情況,但是糾錯電路會更加復雜。

權衡TMR和EDAC的優缺點,通常會在邏輯電路設計中使用TMR,在存儲器讀寫電路中使用EDAC。

CMOS雙二階開關電容有源濾波器芯片,應用廣泛。其內部電路結構如示。芯片內部包含兩個獨立且性能相同的二階濾波單元,可通過外圍匹配的電阻電容構成級聯反饋網絡,設計4階、6階、8階甚至更高階的多級反饋帶通濾波器,可實現切比雪夫、巴特沃斯、貝塞爾、橢圓等類型。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607