PCB匹配設計對焊接質量因素輸出電容值為100μF/A

發布時間:2021/11/17 18:11:00 訪問次數:463

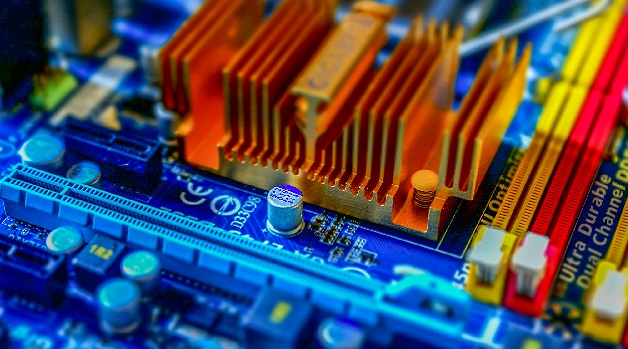

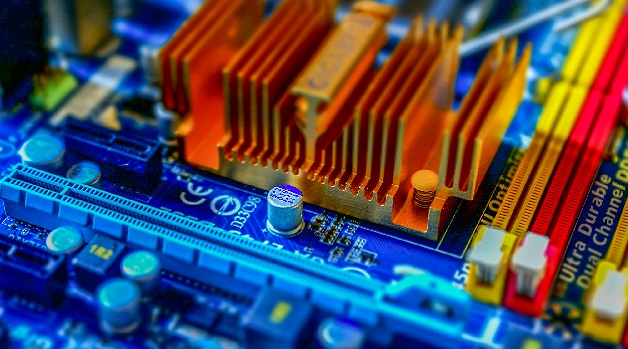

通過對不同廠家PCB、電解電容產品單體結構分析,并從焊接失效機理、失效因素、結構可靠性、工藝等多方面進行核實,對改善后產品單體結構可靠性對比論證,發現需從器件本身進行整改。

改善后進行對比分析,整改后效果明顯。對電解電容焊片式引腳工藝調整,對分析評估類似焊片式引腳提升焊接可靠性有良好借鑒作用。

焊接異常有多方面因素,生產過程設備、PCB 匹配設計對焊接質量因素同樣重要。通過此次整改,在引入開發時需對電解電容焊片式引腳電解電容焊接可靠性進行充分驗證評估,并跟蹤生產過程收集整理數據,以提高產品的結構可靠性,提升電子元件焊接一次通過率。

全新超低成本、超低功耗現場可編程門陣列(FPGA)產品家族。

ForgeFPGA產品將服務于需要低于5,000邏輯門的應用,其初始器件尺寸為1K和2K查找表(LUT)。首批產品待機功率預計低于20μA,約為競爭對手產品功耗的一半。

用戶將能夠免費下載開發軟件,且無需支付授權費。該軟件提供兩種開發模式,以適應新老FPGA開發人員的需求:即使用基于原理圖捕獲開發流程的“宏單元模式”,以及為資深FPGA設計師帶來熟悉Verilog環境的“HDL”模式。

性能:

外形尺寸:127.0mm×88.9mm×17.3mm(L×W×H)

寬輸入電壓范圍

多種電壓輸出,單、雙路輸出

超薄、小型化設計

高效率、高功率密度

金屬殼封裝

(素材來源:ttic和eccn.如涉版權請聯系刪除。特別感謝)

通過對不同廠家PCB、電解電容產品單體結構分析,并從焊接失效機理、失效因素、結構可靠性、工藝等多方面進行核實,對改善后產品單體結構可靠性對比論證,發現需從器件本身進行整改。

改善后進行對比分析,整改后效果明顯。對電解電容焊片式引腳工藝調整,對分析評估類似焊片式引腳提升焊接可靠性有良好借鑒作用。

焊接異常有多方面因素,生產過程設備、PCB 匹配設計對焊接質量因素同樣重要。通過此次整改,在引入開發時需對電解電容焊片式引腳電解電容焊接可靠性進行充分驗證評估,并跟蹤生產過程收集整理數據,以提高產品的結構可靠性,提升電子元件焊接一次通過率。

全新超低成本、超低功耗現場可編程門陣列(FPGA)產品家族。

ForgeFPGA產品將服務于需要低于5,000邏輯門的應用,其初始器件尺寸為1K和2K查找表(LUT)。首批產品待機功率預計低于20μA,約為競爭對手產品功耗的一半。

用戶將能夠免費下載開發軟件,且無需支付授權費。該軟件提供兩種開發模式,以適應新老FPGA開發人員的需求:即使用基于原理圖捕獲開發流程的“宏單元模式”,以及為資深FPGA設計師帶來熟悉Verilog環境的“HDL”模式。

性能:

外形尺寸:127.0mm×88.9mm×17.3mm(L×W×H)

寬輸入電壓范圍

多種電壓輸出,單、雙路輸出

超薄、小型化設計

高效率、高功率密度

金屬殼封裝

(素材來源:ttic和eccn.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607