2.5D/3DIC封裝分析方案Metis與新思3DIC Compiler設計流程

發布時間:2022/1/6 13:11:30 訪問次數:668

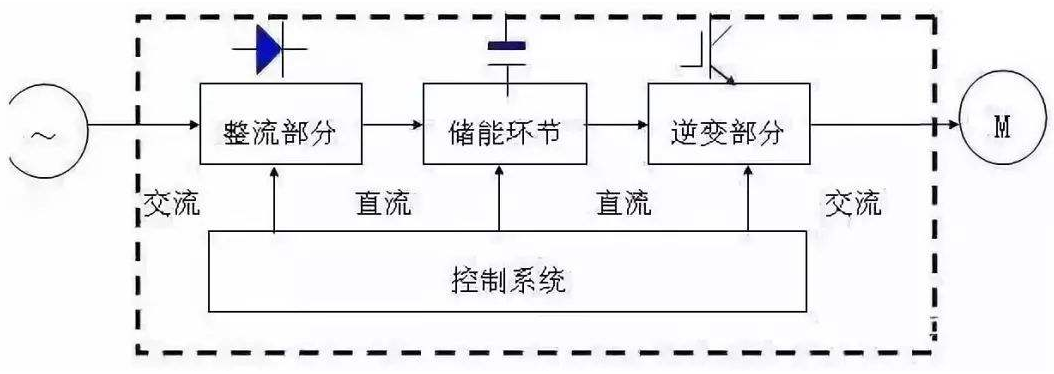

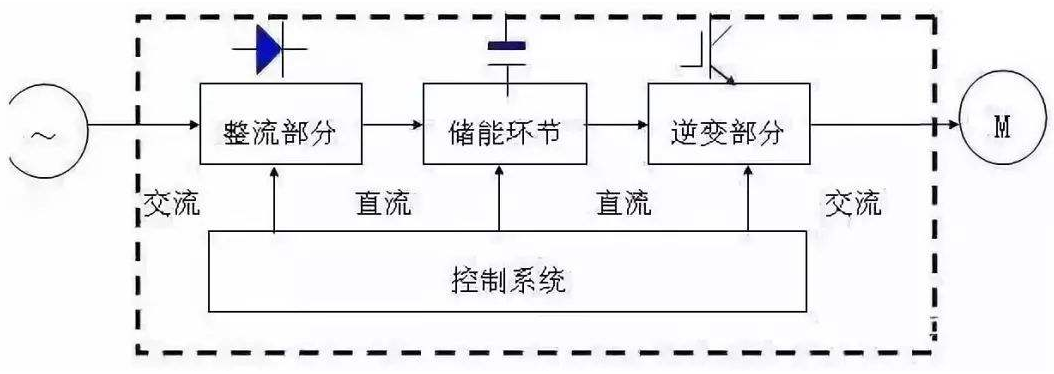

3DIC將不同工藝制程、不同性質的芯片以三維堆疊的方式整合在一個封裝體內,提供性能、功耗、面積和成本的優勢,能夠為5G移動、HPC、AI、汽車電子等領先應用提供更高水平的集成、更高性能的計算和更多的內存訪問。

然而,3DIC作為一個新的領域,之前并沒有成熟的設計分析解決方案,使用傳統的脫節的點工具和流程對設計收斂會帶來巨大的挑戰,而對信號、電源完整性分析的需求也隨著垂直堆疊的芯片而爆發式增長。

HTTP1.1添加了一些擴展(就是在GET.POST,HEAD等幾個HTTP標準方法以外添加了一些新的方法),使得應用程序可以直接將文件寫到WebServer±,從而替代傳統的FTP傳輸文件模式。

存儲平臺通過在Hadoop上部署WebDAV,可實現客戶端(應用服務器)對服務器端(Hadoop節點服務器)的復制和移動文件,并可進行多用戶同時讀取一個文件等操作。

3DIC先進封裝設計分析全流程EDA平臺,將芯和2.5D/3DIC先進封裝分析方案Metis與新思3DIC Compiler現有的設計流程無縫結合,突破了傳統封裝技術的極限,能同時支持芯片間幾十萬根數據通道的互聯。

當負載從脈沖頻率調制 (PFM) 逐漸向脈寬調制 (PWM) 轉換點爬升時,客戶將會看到非常流暢的無縫轉換,不同于傳統架構常見的輸出電壓過沖。

這對于在150mA范圍出現的轉換點尤其重要,因為許多負載在這個范圍耗費了大量的時間。

(素材來源:21ic和eccn.如涉版權請聯系刪除。特別感謝)

3DIC將不同工藝制程、不同性質的芯片以三維堆疊的方式整合在一個封裝體內,提供性能、功耗、面積和成本的優勢,能夠為5G移動、HPC、AI、汽車電子等領先應用提供更高水平的集成、更高性能的計算和更多的內存訪問。

然而,3DIC作為一個新的領域,之前并沒有成熟的設計分析解決方案,使用傳統的脫節的點工具和流程對設計收斂會帶來巨大的挑戰,而對信號、電源完整性分析的需求也隨著垂直堆疊的芯片而爆發式增長。

HTTP1.1添加了一些擴展(就是在GET.POST,HEAD等幾個HTTP標準方法以外添加了一些新的方法),使得應用程序可以直接將文件寫到WebServer±,從而替代傳統的FTP傳輸文件模式。

存儲平臺通過在Hadoop上部署WebDAV,可實現客戶端(應用服務器)對服務器端(Hadoop節點服務器)的復制和移動文件,并可進行多用戶同時讀取一個文件等操作。

3DIC先進封裝設計分析全流程EDA平臺,將芯和2.5D/3DIC先進封裝分析方案Metis與新思3DIC Compiler現有的設計流程無縫結合,突破了傳統封裝技術的極限,能同時支持芯片間幾十萬根數據通道的互聯。

當負載從脈沖頻率調制 (PFM) 逐漸向脈寬調制 (PWM) 轉換點爬升時,客戶將會看到非常流暢的無縫轉換,不同于傳統架構常見的輸出電壓過沖。

這對于在150mA范圍出現的轉換點尤其重要,因為許多負載在這個范圍耗費了大量的時間。

(素材來源:21ic和eccn.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607