LXT988QC真值表及兩個觸發器所要求的激勵信號

發布時間:2020/1/22 19:03:27 訪問次數:3256

lxt988qc圖7例6.3.2狀態分配后,特性表提供了在不同現態和輸人條件下所對應的的狀態圖次態。而在時序電路設計時,狀態表已列出現態到次態的轉換關系,希望推導出觸發器的激勵條件。所以需將特性表做適當變換,以給定的狀態轉換為條件,列出所需求的輸入信號。這樣的表格稱為激勵表。根據表5.4.2建立的jk觸發器激勵表如表6.3,4所示。表中的×表示其邏輯值與該行的狀態轉換無關。

表6.3.4器的激勵表,根據圖6.3,7和表6.3.4可以列出狀態轉換真值表及兩個觸發器所要求的激勵信號,如表6,3,5所示c據此,分別畫出兩個觸發器的輸人j、Κ和電路輸出y的卡諾圖,如圖6,3.8所示。圖中,不使用的狀態均以無關項×填人。化簡后得到激勵方程組和輸出方程

fj=qa k1=a

tjo=a -ko=y=o1a

同步時序邏輯電路的設計里采取00→01→11→00的變化順序,可能會使其中的組合電路相對簡單。于是,令c=00,a=01,c=11,得到狀態分配后的狀態圖,如圖6.3,7所示。

選擇觸發器類型,用小規模集成的觸發器芯片設計時序電路時,選用邏輯功能較強的jk觸發器可能得到較簡化的組合電路。

確定激勵方程組和輸出方程組,用jk觸發器設計時序電路時,電路的激勵圖6.3.10例6,始狀態表,根據圖狀態化簡.

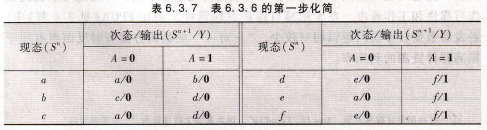

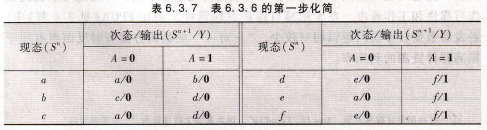

觀察表6.3.6發第一步化簡的結果:出欄中的狀態g。

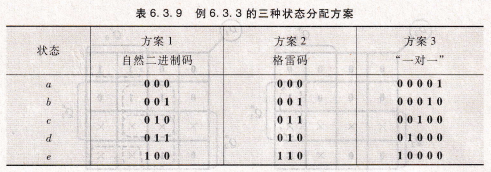

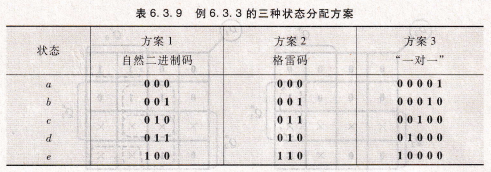

不同步時序邏輯電路的設計,,以/y現態(sn)次態/輸出(sn+/y)次態/輸出(sn+1/y),現態(sn)a=1次態/輸出(sn+1/y)現態次態/輸出(s″+l/y).的三種狀態分配方案,本例按狀態配狀態的

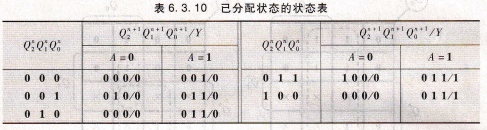

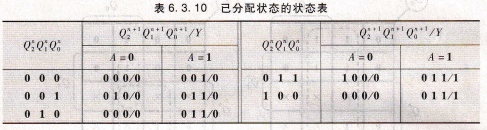

確定激勵方程組和輸出方程組,該電路需要用3個d觸發器實現,它們的輸出分別為q2、0l、o0。于是,由表6,3.10可得狀態轉換真值表,如表6.3.11所示。

由于d觸發器特性方程為qn+1=d,所以根據表6,3,11,可以直接畫出d2、d1、do和y的卡諾圖如圖6.3.12所示,未應用的狀態可作為無關項×填人。

表6.3,11 例6,3,3的狀態轉換真值表q+1(d2) ql+1(di) q1(do)自然二進制碼.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

lxt988qc圖7例6.3.2狀態分配后,特性表提供了在不同現態和輸人條件下所對應的的狀態圖次態。而在時序電路設計時,狀態表已列出現態到次態的轉換關系,希望推導出觸發器的激勵條件。所以需將特性表做適當變換,以給定的狀態轉換為條件,列出所需求的輸入信號。這樣的表格稱為激勵表。根據表5.4.2建立的jk觸發器激勵表如表6.3,4所示。表中的×表示其邏輯值與該行的狀態轉換無關。

表6.3.4器的激勵表,根據圖6.3,7和表6.3.4可以列出狀態轉換真值表及兩個觸發器所要求的激勵信號,如表6,3,5所示c據此,分別畫出兩個觸發器的輸人j、Κ和電路輸出y的卡諾圖,如圖6,3.8所示。圖中,不使用的狀態均以無關項×填人。化簡后得到激勵方程組和輸出方程

fj=qa k1=a

tjo=a -ko=y=o1a

同步時序邏輯電路的設計里采取00→01→11→00的變化順序,可能會使其中的組合電路相對簡單。于是,令c=00,a=01,c=11,得到狀態分配后的狀態圖,如圖6.3,7所示。

選擇觸發器類型,用小規模集成的觸發器芯片設計時序電路時,選用邏輯功能較強的jk觸發器可能得到較簡化的組合電路。

確定激勵方程組和輸出方程組,用jk觸發器設計時序電路時,電路的激勵圖6.3.10例6,始狀態表,根據圖狀態化簡.

觀察表6.3.6發第一步化簡的結果:出欄中的狀態g。

不同步時序邏輯電路的設計,,以/y現態(sn)次態/輸出(sn+/y)次態/輸出(sn+1/y),現態(sn)a=1次態/輸出(sn+1/y)現態次態/輸出(s″+l/y).的三種狀態分配方案,本例按狀態配狀態的

確定激勵方程組和輸出方程組,該電路需要用3個d觸發器實現,它們的輸出分別為q2、0l、o0。于是,由表6,3.10可得狀態轉換真值表,如表6.3.11所示。

由于d觸發器特性方程為qn+1=d,所以根據表6,3,11,可以直接畫出d2、d1、do和y的卡諾圖如圖6.3.12所示,未應用的狀態可作為無關項×填人。

表6.3,11 例6,3,3的狀態轉換真值表q+1(d2) ql+1(di) q1(do)自然二進制碼.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607