一連串的脈沖可以在電路的輸人端產生累計效應

發布時間:2018/12/31 17:24:36 訪問次數:1002

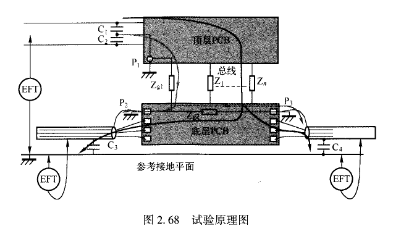

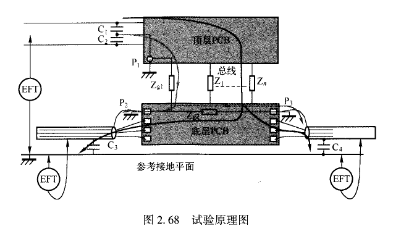

一連串的脈沖可以在電路的輸人端產生累計效應,使干擾電平的幅度最終超過電路的噪聲門限。從這個機理上看,脈沖串的周期越短,對電路的影響越大。 KAA3528ESGC-CIS脈沖串中的每個脈沖相距很近時,電路的輸人電容沒有足夠的時間放電,就又開始新的充電,容易達到較高的電平。當這個電平足以影響電路正常工作時,系統就表現出受到干擾。實際上在EFT/B試驗中,整個試驗的原理圖如圖2..68所示。

圖2.68,EFT為干擾源,測試時,干擾源分別施加在DC電源口、“胛al cable1上與⒍gnal cable2上;CI、C2是EUT電源輸人口的Y電容;C3、C4是信號電纜對參考地的分布電容;P1、P2、P3分別是三個可以接地的接地點;頂層PCB與底層PCB分別是這個EUT中的放置在上面的PCB和放置在下面的PCB,兩板信號之間通過排針互連。Zl~ZⅡ表示信號排針的阻抗;Zgl表示地排針的阻抗;Zg2表示P2、P3之間互連PCB印制布線的阻抗。

EFT/B干擾造成設備失效的機理是利用干擾信號對設備線路結電容的充電,在上面的能量積累到一定程度之后,就可能引起線路(乃至系統)出錯。這個結電容充電的過程也就是EⅢ/B干擾的共模電流流過EUT的過程,流過EUT的共模電流的大小和時間直接決定了EFT/B試驗結果。

一連串的脈沖可以在電路的輸人端產生累計效應,使干擾電平的幅度最終超過電路的噪聲門限。從這個機理上看,脈沖串的周期越短,對電路的影響越大。 KAA3528ESGC-CIS脈沖串中的每個脈沖相距很近時,電路的輸人電容沒有足夠的時間放電,就又開始新的充電,容易達到較高的電平。當這個電平足以影響電路正常工作時,系統就表現出受到干擾。實際上在EFT/B試驗中,整個試驗的原理圖如圖2..68所示。

圖2.68,EFT為干擾源,測試時,干擾源分別施加在DC電源口、“胛al cable1上與⒍gnal cable2上;CI、C2是EUT電源輸人口的Y電容;C3、C4是信號電纜對參考地的分布電容;P1、P2、P3分別是三個可以接地的接地點;頂層PCB與底層PCB分別是這個EUT中的放置在上面的PCB和放置在下面的PCB,兩板信號之間通過排針互連。Zl~ZⅡ表示信號排針的阻抗;Zgl表示地排針的阻抗;Zg2表示P2、P3之間互連PCB印制布線的阻抗。

EFT/B干擾造成設備失效的機理是利用干擾信號對設備線路結電容的充電,在上面的能量積累到一定程度之后,就可能引起線路(乃至系統)出錯。這個結電容充電的過程也就是EⅢ/B干擾的共模電流流過EUT的過程,流過EUT的共模電流的大小和時間直接決定了EFT/B試驗結果。

上一篇:怎樣接地才有利于EMC

公網安備44030402000607

公網安備44030402000607