RMCF0603JT7R50 噪聲容限

發布時間:2019/10/10 20:29:14 訪問次數:1882

RMCF0603JT7R50噪聲容限表示門電路的抗干擾能力。二值數字邏輯電路的優點在于它的輸人信號允許一定的容差。在數字系統中,各邏輯電路之間的連線可能會受到各種噪聲的干擾,例如信號傳輸引起的噪聲,信號的高低電平轉換引起的噪聲,或者鄰近開關信號所引起的隨機脈沖的噪聲。這些噪聲會疊加在工作信號上,只要其幅度不超過邏輯電平允許的最小值或最大值,則輸出邏輯狀態不會受影響。通常將這個最大噪聲幅度稱為噪聲容限。電路的噪聲容限愈大,其抗干擾能力愈強。

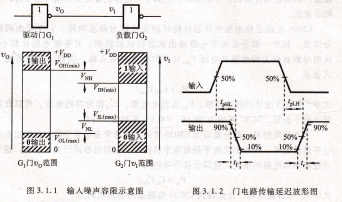

圖3.1.1所示為噪聲容限定義的示意圖。前一級驅動門電路的輸出,就是后一級負載門電路的輸人。當前一級輸出高電平的最小值仍能滿足后級高電平輸人最小值時,輸人高電平的噪聲容限為

VNH=V0H(min)-VIH(mIN) (3・1.1)

同理得出,輸人低電平的噪聲容限

VNL=V1L(max)-VoL(max) (3・1・2)

根據74HC系列CMOS集成電路在5V典型工作電壓時的參數,求得其輸入高、低電平的噪聲容限分別為:

高電平的噪聲容限 yNH=y。n(min)^ym(min)=4・9v-3.5V=1.4V

低電平的噪聲容限 ‰L=【IL(m ax)^y。“m ax)=1・5Ⅴˉ0.1Ⅴ=1.4V

其他CMOs系列的高、低電平的噪聲容限列于表3.1.2中。

傳輸延遲時間

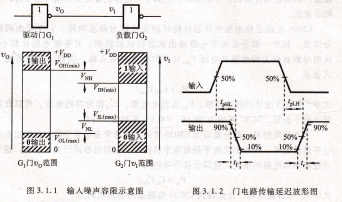

傳輸延遲時間是表征門電路開關速度的參數,它說明門電路在輸入脈沖波形的作用下,其輸出波形相對于輸入波形延遲了多長的時間。當門電路的輸人端加人一脈沖波形,其相應的輸出波形如圖3.1.2所示。通常輸出波形下降沿、上升沿的中點與輸入波形對應沿中點之間的時間間隔,分別用莎pLH和JpHL。

RMCF0603JT7R50噪聲容限表示門電路的抗干擾能力。二值數字邏輯電路的優點在于它的輸人信號允許一定的容差。在數字系統中,各邏輯電路之間的連線可能會受到各種噪聲的干擾,例如信號傳輸引起的噪聲,信號的高低電平轉換引起的噪聲,或者鄰近開關信號所引起的隨機脈沖的噪聲。這些噪聲會疊加在工作信號上,只要其幅度不超過邏輯電平允許的最小值或最大值,則輸出邏輯狀態不會受影響。通常將這個最大噪聲幅度稱為噪聲容限。電路的噪聲容限愈大,其抗干擾能力愈強。

圖3.1.1所示為噪聲容限定義的示意圖。前一級驅動門電路的輸出,就是后一級負載門電路的輸人。當前一級輸出高電平的最小值仍能滿足后級高電平輸人最小值時,輸人高電平的噪聲容限為

VNH=V0H(min)-VIH(mIN) (3・1.1)

同理得出,輸人低電平的噪聲容限

VNL=V1L(max)-VoL(max) (3・1・2)

根據74HC系列CMOS集成電路在5V典型工作電壓時的參數,求得其輸入高、低電平的噪聲容限分別為:

高電平的噪聲容限 yNH=y。n(min)^ym(min)=4・9v-3.5V=1.4V

低電平的噪聲容限 ‰L=【IL(m ax)^y。“m ax)=1・5Ⅴˉ0.1Ⅴ=1.4V

其他CMOs系列的高、低電平的噪聲容限列于表3.1.2中。

傳輸延遲時間

傳輸延遲時間是表征門電路開關速度的參數,它說明門電路在輸入脈沖波形的作用下,其輸出波形相對于輸入波形延遲了多長的時間。當門電路的輸人端加人一脈沖波形,其相應的輸出波形如圖3.1.2所示。通常輸出波形下降沿、上升沿的中點與輸入波形對應沿中點之間的時間間隔,分別用莎pLH和JpHL。

公網安備44030402000607

公網安備44030402000607