0009521065 TN和TP的柵極等效電容

發布時間:2019/10/10 22:32:44 訪問次數:1935

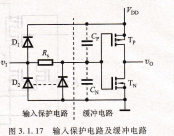

0009521065Sio2層,小于0.1 um,極易被擊穿。而輸人電阻高達1012Ω以上,輸人電容為幾皮法。電路在使用前輸人端是懸空的,只要外界有很小的靜電源,都會在輸入端積累電荷而將柵極擊穿。因此,在CMOs電路的輸入端都增加了二極管保護電路。圖3.1.17所示為輸人保護電路和輸人緩沖電路。圖中CN和CP分別表示TN和TP的柵極等效電容,D1和D2是正向導通壓降%F=0.5~0・7Ⅴ的二極管,D2是分布式二極管結構,用虛線和兩個二極管表示。這種分布式二極管結構可以通過較大的電流,使得輸°I入引腳上的靜電荷得以釋放,從而保護了MOS管的柵極絕緣層。二極管的反向擊穿電壓約為30V,小于柵極sio2層的擊穿電壓。

輸入電壓在正常范圍內(0≤ vI≤yDD),保護電路不起作用 。當oI>(/DD+%F或vI(-7DF時 ,MOs管的柵極電位,保護電路不起作用。當vI)(7DD+yDF)或v1(-7DF時,MOs管的柵極電位被限制在一yDF~(yDD+/DF)之間,使柵極的sio2層不會被擊穿。如果輸人電平發生突變時的過沖電壓超出上述輸入電壓范圍,可能使二極管D1或D2首先被擊穿。當過沖時間較短時,二極管仍能恢復工作;當過沖時間較長或過沖電壓很大時,可能損壞二極管,進而使MOs管柵極被擊穿。

另外,電阻Rs和MOs管的柵極電容組成積分網絡,使輸人信號的過沖電壓延遲一段時間才作用到柵極上,而且幅度有所衰減。為減小這種延遲對電路動態性能的影響,Rs值不宜過大,一般多晶硅柵極電阻為250Ω。

邏輯門電路輸出端也接人靜電保護二極管,確保輸出不超出正常的工作范圍。

CMOs邏輯門的緩沖電路,圖3,1.18所示為帶緩沖級的CMOs與非門電Ⅱ路的邏輯符號。由于輸人、輸出端加了反相器作為緩沖電路,所以電路的邏輯功能也發生了變化。圖中的基本邏輯功能電路是或非門(見圖3.1.14),圖3.1.18 帶緩沖級的CMOs與增加了緩沖器后的邏輯功能為與非功能,即

L=A+B=A・B

CMOS漏極開路門和三態輸出門電路,前面討論了具有輸入、輸出緩沖電路的CMOs集成電路。如果從輸出端看,還有另外兩種輸出結構的CMOs門電路,漏極開路門和三態輸出門.

0009521065Sio2層,小于0.1 um,極易被擊穿。而輸人電阻高達1012Ω以上,輸人電容為幾皮法。電路在使用前輸人端是懸空的,只要外界有很小的靜電源,都會在輸入端積累電荷而將柵極擊穿。因此,在CMOs電路的輸入端都增加了二極管保護電路。圖3.1.17所示為輸人保護電路和輸人緩沖電路。圖中CN和CP分別表示TN和TP的柵極等效電容,D1和D2是正向導通壓降%F=0.5~0・7Ⅴ的二極管,D2是分布式二極管結構,用虛線和兩個二極管表示。這種分布式二極管結構可以通過較大的電流,使得輸°I入引腳上的靜電荷得以釋放,從而保護了MOS管的柵極絕緣層。二極管的反向擊穿電壓約為30V,小于柵極sio2層的擊穿電壓。

輸入電壓在正常范圍內(0≤ vI≤yDD),保護電路不起作用 。當oI>(/DD+%F或vI(-7DF時 ,MOs管的柵極電位,保護電路不起作用。當vI)(7DD+yDF)或v1(-7DF時,MOs管的柵極電位被限制在一yDF~(yDD+/DF)之間,使柵極的sio2層不會被擊穿。如果輸人電平發生突變時的過沖電壓超出上述輸入電壓范圍,可能使二極管D1或D2首先被擊穿。當過沖時間較短時,二極管仍能恢復工作;當過沖時間較長或過沖電壓很大時,可能損壞二極管,進而使MOs管柵極被擊穿。

另外,電阻Rs和MOs管的柵極電容組成積分網絡,使輸人信號的過沖電壓延遲一段時間才作用到柵極上,而且幅度有所衰減。為減小這種延遲對電路動態性能的影響,Rs值不宜過大,一般多晶硅柵極電阻為250Ω。

邏輯門電路輸出端也接人靜電保護二極管,確保輸出不超出正常的工作范圍。

CMOs邏輯門的緩沖電路,圖3,1.18所示為帶緩沖級的CMOs與非門電Ⅱ路的邏輯符號。由于輸人、輸出端加了反相器作為緩沖電路,所以電路的邏輯功能也發生了變化。圖中的基本邏輯功能電路是或非門(見圖3.1.14),圖3.1.18 帶緩沖級的CMOs與增加了緩沖器后的邏輯功能為與非功能,即

L=A+B=A・B

CMOS漏極開路門和三態輸出門電路,前面討論了具有輸入、輸出緩沖電路的CMOs集成電路。如果從輸出端看,還有另外兩種輸出結構的CMOs門電路,漏極開路門和三態輸出門.

公網安備44030402000607

公網安備44030402000607