LM116H/883C CMOS門電路是否過載

發布時間:2019/10/12 17:55:35 訪問次數:1663

LM116H/883CCMOs門驅動TTL門,在CMOS電路的供電電源為十5Ⅴ時,兩者的邏輯電平參數可滿足式(3,6.3)和式(3.6.4),不需另加接口電路,僅按電流大小計算出扇出數即可。

圖3.6.1表示CMOs門驅動TTL門的簡單電路。當CMOS門的輸出為高電平時,它為TTL負載提供拉電流,反之則提供灌電流。

例3,6,1 用一個74HC00與非門電路驅動一個74系列TTL反相器和6個74LS系列邏輯門電路。試驗算此時的CMOS門電路是否過載?已知74系列TTL反相器的參數rlL(m ax)=1.6 mA,rm(n ax)=o.04 mA。其他參數可查附錄A。

解:由附錄A查得74HC00和74LS系列參數如下:

灌電流情況下,74HC00門電路的f。L(max)=4 mA,74LS門的輸人電流了IL(max)=0・4 mA,總的輸人電流為74系列TTL反相器和74LS系列邏輯門電路輸入電流之和,即fIL(t。tal)=1・6 mA+6×0.4 mA=4 mA,滿足式(3.6.1)的條件。

拉電流情況下,74HC00門電路的IOH(max)=4 mA,74LS系列的rm(max)

=0.02mA,因此,總的輸入電流Jm(tOtal)=0.04mA+6*0.02mA=0.16mA,滿足式(3.6.2)的條件。

根據以上分析,CMOs驅動TTL門電路未過載,但是灌電流情況剛剛滿足條件,在實際電路設計中要考慮留出一定的余量,即增加帶灌電流的能力。可以在驅動門和負載門之間增加一個驅動器,由于TTL系列ioL(max)比CMOS的ioL(max)大得多,最簡單的辦法是CMOS門后面加一個TTL系列的同相緩沖器,再用這個緩沖器驅動上述1個74系列TTL反相器和6個74LS系列邏輯門電路。

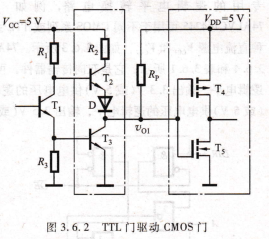

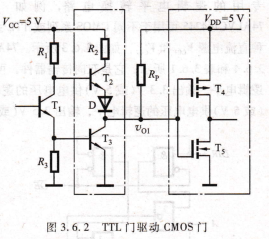

TTL門驅動CMOs門,用TTL電路驅動74HCT系列CMOS電路時,由附錄A可知,由于高、低電平參數兼容,不需另加接口電路。當74HC系列CMOs為負載器件時,TTL輸出低電平參數與74HC的輸入低電平參數兼容,但是高電平參數不兼容。例如74LS系列的%H(n”n)為2.7V,而74HC系列的7IH(min)為3.5Ⅴ。

為了解決這一矛盾,常采用如圖3.6.2所示的方法,在TTL的輸出端與+5V電源之間接一個上拉電阻Rp’上拉電阻的值取決于負載器件的數目以及TTL和CMOS的電流參數,可以用OC門外接上拉電阻的計算方法進行計算。但必須注意,此時VOH(min)

式中,IOz為TTL電路輸出高電平時,輸出管截止時的漏電流,IIH(TOtal)為流人全部CMOs負載電路的電流,這兩個電流的數值都很小,如果Rp取值不太大,U01將被提高至接近VDD。

LM116H/883CCMOs門驅動TTL門,在CMOS電路的供電電源為十5Ⅴ時,兩者的邏輯電平參數可滿足式(3,6.3)和式(3.6.4),不需另加接口電路,僅按電流大小計算出扇出數即可。

圖3.6.1表示CMOs門驅動TTL門的簡單電路。當CMOS門的輸出為高電平時,它為TTL負載提供拉電流,反之則提供灌電流。

例3,6,1 用一個74HC00與非門電路驅動一個74系列TTL反相器和6個74LS系列邏輯門電路。試驗算此時的CMOS門電路是否過載?已知74系列TTL反相器的參數rlL(m ax)=1.6 mA,rm(n ax)=o.04 mA。其他參數可查附錄A。

解:由附錄A查得74HC00和74LS系列參數如下:

灌電流情況下,74HC00門電路的f。L(max)=4 mA,74LS門的輸人電流了IL(max)=0・4 mA,總的輸人電流為74系列TTL反相器和74LS系列邏輯門電路輸入電流之和,即fIL(t。tal)=1・6 mA+6×0.4 mA=4 mA,滿足式(3.6.1)的條件。

拉電流情況下,74HC00門電路的IOH(max)=4 mA,74LS系列的rm(max)

=0.02mA,因此,總的輸入電流Jm(tOtal)=0.04mA+6*0.02mA=0.16mA,滿足式(3.6.2)的條件。

根據以上分析,CMOs驅動TTL門電路未過載,但是灌電流情況剛剛滿足條件,在實際電路設計中要考慮留出一定的余量,即增加帶灌電流的能力。可以在驅動門和負載門之間增加一個驅動器,由于TTL系列ioL(max)比CMOS的ioL(max)大得多,最簡單的辦法是CMOS門后面加一個TTL系列的同相緩沖器,再用這個緩沖器驅動上述1個74系列TTL反相器和6個74LS系列邏輯門電路。

TTL門驅動CMOs門,用TTL電路驅動74HCT系列CMOS電路時,由附錄A可知,由于高、低電平參數兼容,不需另加接口電路。當74HC系列CMOs為負載器件時,TTL輸出低電平參數與74HC的輸入低電平參數兼容,但是高電平參數不兼容。例如74LS系列的%H(n”n)為2.7V,而74HC系列的7IH(min)為3.5Ⅴ。

為了解決這一矛盾,常采用如圖3.6.2所示的方法,在TTL的輸出端與+5V電源之間接一個上拉電阻Rp’上拉電阻的值取決于負載器件的數目以及TTL和CMOS的電流參數,可以用OC門外接上拉電阻的計算方法進行計算。但必須注意,此時VOH(min)

式中,IOz為TTL電路輸出高電平時,輸出管截止時的漏電流,IIH(TOtal)為流人全部CMOs負載電路的電流,這兩個電流的數值都很小,如果Rp取值不太大,U01將被提高至接近VDD。

熱門點擊

熱門點擊

- 電壓一時間型分段器X、y時限的整定原則

- LA5112N 復雜的數字系統制作

- 饋線自動化的功能與類型

- 7次諧波的實用判據

- MAX6805US44D3+T CMOS集成

- 穩態實驗主要是從有無整流負載

- 三電源點的多分段多聯絡接線故障

- 開閉所DTU與饋線終端FTU的比較

- LM4852LQ MOS管的開關特性

- 對半分割檢索算法

推薦技術資料

推薦技術資料

- 泰克新發布的DSA830

- 泰克新發布的DSA8300在一臺儀器中同時實現時域和頻域分析,DS... [詳細]

公網安備44030402000607

公網安備44030402000607