LT1328BCS8用或非門構成基本

發布時間:2019/10/14 17:55:19 訪問次數:1555

LT1328BCS8為什么圖5,1.2所示的電路能長期保持狀態不變?

從模擬分析的角度看,圖5.1.2所示的電路構成正反饋環路,為什么它不會產生自激振蕩?

鎖存器和觸發器①是構成各種時序電路的存儲單元電路,其共同特點是都具有0和1兩種穩定狀態,一旦狀態被確定,就能自行保持,即長期存儲1位二進制碼,直到有外部信號作用時才有可能改變。鎖存器是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態。而由不同鎖存器構成的觸發器則是一種對脈沖邊沿敏感的存儲電路,它們只有在作為觸發信號的時鐘脈沖上升沿或下降沿的變化瞬間才能改變狀態。

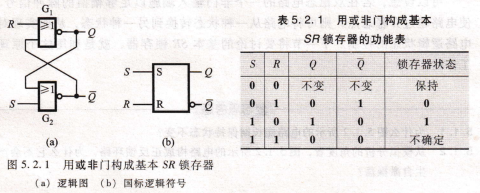

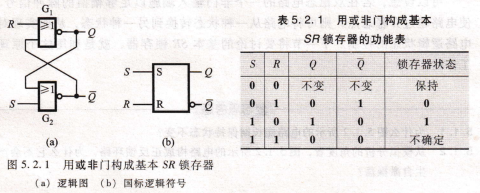

SR鎖存器,基本SR鎖存器,將圖5.1.2中雙穩態電路的非門替換為或非門,則構成圖5.2,1(a)所示的基本SR鎖存器①。它是―種具有簡單功能的雙穩態存儲電路,圖5.2,1(b)所示為其邏輯符號。電路有兩個輸人端,其中s端稱為置位(1)端,R端稱為復位端或清零(0)端。按照邏輯圖,可以列出輸出端Q和口的邏輯表達式

Q=R+0 (5.2.1)

Q=s+O (5.2.2)

根據以上兩式,可得基本sR鎖存器的功能表,如表5.2.1所示。

用或非門構成基本,SR鎖存器的功能表,用或非門構成基本sR鎖存器(a)邏輯圖 (b)國標邏輯符號.

當s=R=0時,對應表5.2.1的第1行。根據式(5.2.1)和式(5.2.2),這兩個輸入信號對兩或非門的輸出o和回不起作用,電路狀態保持不變,功能與圖5.1.2的雙穩態電路相同,可存儲1位二進制數據。

表5.2.1的第2、3行分別為鎖存器的置0和置1操作。在Q=0,R=0的條件下 ,當s端出現邏輯1電平時 ,Q端輸出電壓下降 ,一旦跨越介穩態點,電路便迅速轉換為Q=1狀態。若原來狀態為Q=1,則s端出現的1電平不改變其狀態。電路是對稱的 ,置0操作將使鎖存器置為Q=0。

當s=R=1時 ,對應表5.2.1中的第4行 。根據上述兩式 ,Q=Q=0,鎖存器處在既非1,又非0的不確定狀態。若s和R同時回到0,則無法預先確定鎖存器將回到1狀態還是0狀態。因此,在正常工作時,輸人信號應遵守本教材以前幾版將鎖存器也稱為觸發器,實際上二者是有差別的,在5.3節還將就此作進一步的討論.

LT1328BCS8為什么圖5,1.2所示的電路能長期保持狀態不變?

從模擬分析的角度看,圖5.1.2所示的電路構成正反饋環路,為什么它不會產生自激振蕩?

鎖存器和觸發器①是構成各種時序電路的存儲單元電路,其共同特點是都具有0和1兩種穩定狀態,一旦狀態被確定,就能自行保持,即長期存儲1位二進制碼,直到有外部信號作用時才有可能改變。鎖存器是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態。而由不同鎖存器構成的觸發器則是一種對脈沖邊沿敏感的存儲電路,它們只有在作為觸發信號的時鐘脈沖上升沿或下降沿的變化瞬間才能改變狀態。

SR鎖存器,基本SR鎖存器,將圖5.1.2中雙穩態電路的非門替換為或非門,則構成圖5.2,1(a)所示的基本SR鎖存器①。它是―種具有簡單功能的雙穩態存儲電路,圖5.2,1(b)所示為其邏輯符號。電路有兩個輸人端,其中s端稱為置位(1)端,R端稱為復位端或清零(0)端。按照邏輯圖,可以列出輸出端Q和口的邏輯表達式

Q=R+0 (5.2.1)

Q=s+O (5.2.2)

根據以上兩式,可得基本sR鎖存器的功能表,如表5.2.1所示。

用或非門構成基本,SR鎖存器的功能表,用或非門構成基本sR鎖存器(a)邏輯圖 (b)國標邏輯符號.

當s=R=0時,對應表5.2.1的第1行。根據式(5.2.1)和式(5.2.2),這兩個輸入信號對兩或非門的輸出o和回不起作用,電路狀態保持不變,功能與圖5.1.2的雙穩態電路相同,可存儲1位二進制數據。

表5.2.1的第2、3行分別為鎖存器的置0和置1操作。在Q=0,R=0的條件下 ,當s端出現邏輯1電平時 ,Q端輸出電壓下降 ,一旦跨越介穩態點,電路便迅速轉換為Q=1狀態。若原來狀態為Q=1,則s端出現的1電平不改變其狀態。電路是對稱的 ,置0操作將使鎖存器置為Q=0。

當s=R=1時 ,對應表5.2.1中的第4行 。根據上述兩式 ,Q=Q=0,鎖存器處在既非1,又非0的不確定狀態。若s和R同時回到0,則無法預先確定鎖存器將回到1狀態還是0狀態。因此,在正常工作時,輸人信號應遵守本教材以前幾版將鎖存器也稱為觸發器,實際上二者是有差別的,在5.3節還將就此作進一步的討論.

公網安備44030402000607

公網安備44030402000607