DRS61-A1A08192 D鎖存器的動態特性

發布時間:2019/10/14 18:10:36 訪問次數:2785

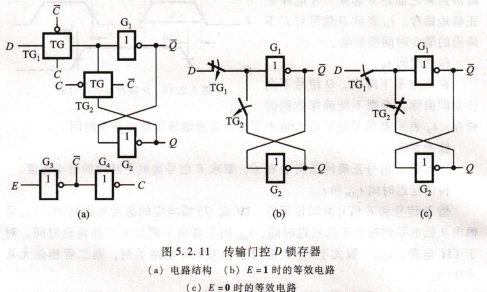

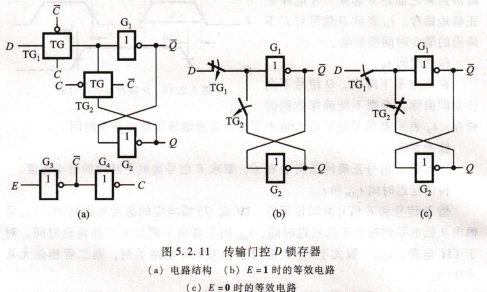

DRS61-A1A08192構成類似于圖5.1.2所示的雙穩態電路,如圖5.2.11(c)所示。由于G1、G2輸人端存在的分布電容對邏輯電平有暫短的保持作用,此時,電路將被鎖定在E信號由1變0前瞬間D信號所確定的狀態。讀者可用表5,2.3來驗證圖5.2.11(a)所示電路的邏輯功能。由于邏輯功能完全相同,所以傳輸門控D鎖存器的邏輯符號仍如圖5.2.10(b)所示。

圖5.2.11(a)所示電路的輸入信號D、E的波形如圖5.2.12虛線上邊所示,畫出O和口的輸出波形。

解:根據圖5.2.11(b)、(c),每當E=1時,o端波形跟隨D端變化,當E跳變為0時,鎖存器保持在跳變前瞬間的狀態,可以畫出Q和口波形,如圖5.2.12虛線下邊所示。

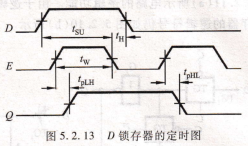

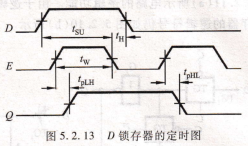

D鎖存器的動態特性,定時圖是表達時序電路動態特性的工具之一,它表達了電路動作過程中,對各輸入信號的時間要求以及輸出對輸入信號的響應時間。圖5.2.13所示是D鎖存器的定時圖,對圖5,2.10(a)和圖5.2.11(a)的電路都是適用的,只是具體參數值有所差異。下面對參數進行說明。

建立時間tsu

數據信號D應在門控信號E下D降沿到來之前建立起來,才能保證正確地鎖存。tsu表示D信號對E下降沿的最少時間提前量。

保持時間tH

在E電平下降后,D信號不允許立即撤除,否則不能確保數據的鎖存。th表示D信號電平在E電平下降后需要繼續保持的最少時間。

脈沖寬度tw

為保證D信號正確傳送到Q和回,要求E信號高電平脈沖的最小寬度。

傳輸延遲時間tpLH和tpHL

指D信號和E信號共同作用后,0(或口)端響應的最大延遲時間。tpLH是輸出從低電平到高電平的延遲時間,rpⅢ則是高電平到低電平的延遲時間。對于TTL電路,莎pLH一般大于rpHL’而對于各CMOS電路系列,則二者相差無幾或相同。

上述ts.、th和tw是對輸入信號的時間要求,tpLH和tpHL是輸出信號的響應時間。在生產廠家提供的數據手冊中,都會給出這些時間關系的明確限度。對于下面將介紹的CMOS八D鎖存器74HCT373,當vcc=4.5V,r=25℃時,要求Jw≥16 ns,rs.≥12 ns,莎Ⅱ≥4 ns,而fpHL和JpLH的典型值為16ns。

在設計工作中對電路的動態特性必須予以充分重視。若不遵守對輸入信號的時間要求,則可能出現錯誤的邏輯輸出;而電路輸出的延遲,將對后面被驅動電路的時間特性產生影響。通常對上述時間關系,要留有充分的余地,特別是電路工作在接近定時極限的高頻條件下更要注意,否則電路長期工作中會發生原因難以查明的偶發性邏輯錯誤,或因環境條件改變(如溫度變化)而出現工作不穩定的情況。

DRS61-A1A08192構成類似于圖5.1.2所示的雙穩態電路,如圖5.2.11(c)所示。由于G1、G2輸人端存在的分布電容對邏輯電平有暫短的保持作用,此時,電路將被鎖定在E信號由1變0前瞬間D信號所確定的狀態。讀者可用表5,2.3來驗證圖5.2.11(a)所示電路的邏輯功能。由于邏輯功能完全相同,所以傳輸門控D鎖存器的邏輯符號仍如圖5.2.10(b)所示。

圖5.2.11(a)所示電路的輸入信號D、E的波形如圖5.2.12虛線上邊所示,畫出O和口的輸出波形。

解:根據圖5.2.11(b)、(c),每當E=1時,o端波形跟隨D端變化,當E跳變為0時,鎖存器保持在跳變前瞬間的狀態,可以畫出Q和口波形,如圖5.2.12虛線下邊所示。

D鎖存器的動態特性,定時圖是表達時序電路動態特性的工具之一,它表達了電路動作過程中,對各輸入信號的時間要求以及輸出對輸入信號的響應時間。圖5.2.13所示是D鎖存器的定時圖,對圖5,2.10(a)和圖5.2.11(a)的電路都是適用的,只是具體參數值有所差異。下面對參數進行說明。

建立時間tsu

數據信號D應在門控信號E下D降沿到來之前建立起來,才能保證正確地鎖存。tsu表示D信號對E下降沿的最少時間提前量。

保持時間tH

在E電平下降后,D信號不允許立即撤除,否則不能確保數據的鎖存。th表示D信號電平在E電平下降后需要繼續保持的最少時間。

脈沖寬度tw

為保證D信號正確傳送到Q和回,要求E信號高電平脈沖的最小寬度。

傳輸延遲時間tpLH和tpHL

指D信號和E信號共同作用后,0(或口)端響應的最大延遲時間。tpLH是輸出從低電平到高電平的延遲時間,rpⅢ則是高電平到低電平的延遲時間。對于TTL電路,莎pLH一般大于rpHL’而對于各CMOS電路系列,則二者相差無幾或相同。

上述ts.、th和tw是對輸入信號的時間要求,tpLH和tpHL是輸出信號的響應時間。在生產廠家提供的數據手冊中,都會給出這些時間關系的明確限度。對于下面將介紹的CMOS八D鎖存器74HCT373,當vcc=4.5V,r=25℃時,要求Jw≥16 ns,rs.≥12 ns,莎Ⅱ≥4 ns,而fpHL和JpLH的典型值為16ns。

在設計工作中對電路的動態特性必須予以充分重視。若不遵守對輸入信號的時間要求,則可能出現錯誤的邏輯輸出;而電路輸出的延遲,將對后面被驅動電路的時間特性產生影響。通常對上述時間關系,要留有充分的余地,特別是電路工作在接近定時極限的高頻條件下更要注意,否則電路長期工作中會發生原因難以查明的偶發性邏輯錯誤,或因環境條件改變(如溫度變化)而出現工作不穩定的情況。

上一篇:IRF632 D鎖存器

公網安備44030402000607

公網安備44030402000607