DRAM內存不同電路中偏置電流的影響

發布時間:2020/12/19 17:40:11 訪問次數:385

內部集成的關鍵功能包括:由低RDSon N溝道功率MOSFET配置成H全橋的完備驅動級電路,為驅動電機繞組提供高達1.2A RMS @ 5-46V驅動;SPI接口用于系統配置和診斷;方向步進控制接口。

DRAM 內存單元必需刷新,避免丟失數據內容。這要求丟失電荷前刷新電容器。刷新內存由內存控制器負責,刷新時間指標因不同DRAM內存而不同。內存控制器對行地址進行僅RAS循環,進行刷新。在僅RAS循環結束時,進行預充電操作,恢復僅RAS循環中尋址的行數據。內存控制器有一個行計數器,其順序生成僅RAS刷新周期所需的所有行地址。

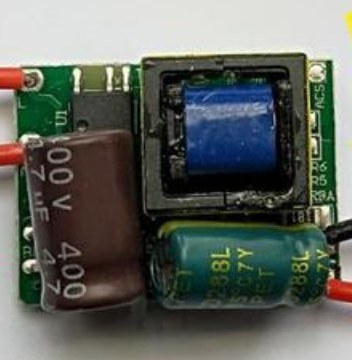

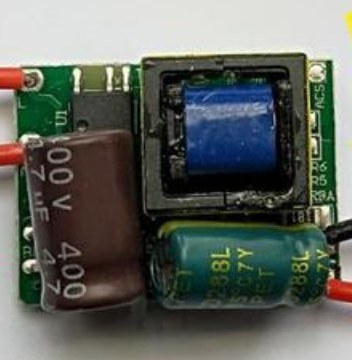

標準包裝:100類別:電容器家庭:薄膜電容器系列:ECQ-V包裝:散裝電容:0.39μF容差:±5%額定電壓 - AC:-額定電壓 - DC:100V介電材料:聚酯,金屬化 - 層疊式ESR(等效串聯電阻):-工作溫度:-40°C ~ 105°C安裝類型:通孔封裝/外殼:徑向大小/尺寸:0.402" 長 x 0.217" 寬(10.20mm x 5.50mm)高度 - 安裝(最大值):0.591"(15.00mm)端接:PC 引腳引線間距:0.197"(5.00mm)應用:通用特性:-其它名稱:ECQV1394JMW

在ADC進行轉換的過程中,采樣保持電路進入保持階段。通常采樣保持電路是靠電容來進行電壓保持的,由于電容和采樣開關中漏電流以及保持電路中偏置電流的影響,使保持的模擬電壓隨時間的延續而有所下降(或上升),其下降的速率就是采樣保持電路的頂級率。

頂級率過大就會影響轉換精度。頂級率和捕獲時間不但與采樣保持電路有關,而且還與外接的保持電容有關,增大電容時,可以減小頂級率,但捕獲時間將增大,因此需要全面考慮。對于模擬輸入電壓變化緩慢的系統,可以不使用采樣保持電路,一般模擬輸入電壓變化不超過1/2LSB時,就可不用。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

內部集成的關鍵功能包括:由低RDSon N溝道功率MOSFET配置成H全橋的完備驅動級電路,為驅動電機繞組提供高達1.2A RMS @ 5-46V驅動;SPI接口用于系統配置和診斷;方向步進控制接口。

DRAM 內存單元必需刷新,避免丟失數據內容。這要求丟失電荷前刷新電容器。刷新內存由內存控制器負責,刷新時間指標因不同DRAM內存而不同。內存控制器對行地址進行僅RAS循環,進行刷新。在僅RAS循環結束時,進行預充電操作,恢復僅RAS循環中尋址的行數據。內存控制器有一個行計數器,其順序生成僅RAS刷新周期所需的所有行地址。

標準包裝:100類別:電容器家庭:薄膜電容器系列:ECQ-V包裝:散裝電容:0.39μF容差:±5%額定電壓 - AC:-額定電壓 - DC:100V介電材料:聚酯,金屬化 - 層疊式ESR(等效串聯電阻):-工作溫度:-40°C ~ 105°C安裝類型:通孔封裝/外殼:徑向大小/尺寸:0.402" 長 x 0.217" 寬(10.20mm x 5.50mm)高度 - 安裝(最大值):0.591"(15.00mm)端接:PC 引腳引線間距:0.197"(5.00mm)應用:通用特性:-其它名稱:ECQV1394JMW

在ADC進行轉換的過程中,采樣保持電路進入保持階段。通常采樣保持電路是靠電容來進行電壓保持的,由于電容和采樣開關中漏電流以及保持電路中偏置電流的影響,使保持的模擬電壓隨時間的延續而有所下降(或上升),其下降的速率就是采樣保持電路的頂級率。

頂級率過大就會影響轉換精度。頂級率和捕獲時間不但與采樣保持電路有關,而且還與外接的保持電容有關,增大電容時,可以減小頂級率,但捕獲時間將增大,因此需要全面考慮。對于模擬輸入電壓變化緩慢的系統,可以不使用采樣保持電路,一般模擬輸入電壓變化不超過1/2LSB時,就可不用。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607