集成10A開關管的12.8V輸出大電流非同步DC-DC升壓IC

發布時間:2021/8/28 22:42:28 訪問次數:1209

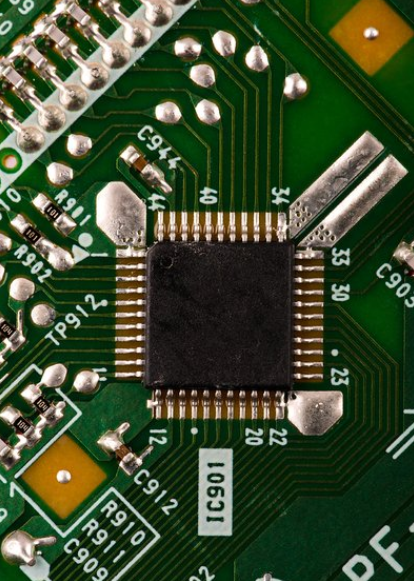

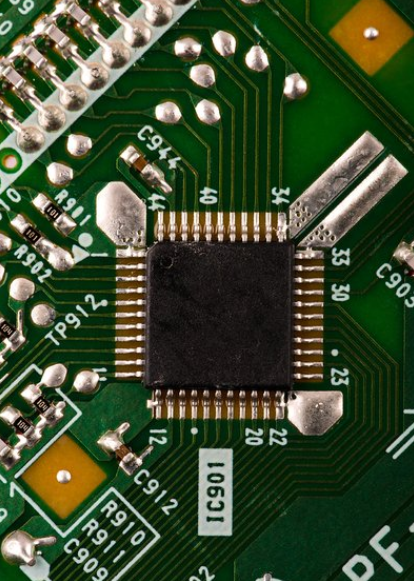

升壓值13V以下的DC-DC升壓應用需求,推廣一款集成10A開關管的12.8V輸出、大電流非同步DC-DC升壓IC:HT7180。

HT7180采用獨到的電路研發技術以及先進的半導體工藝制程,基于SOP8封裝,工作效率高達90%以上,無需外加散熱器,3.7V輸入升壓到12V,可穩定輸出2A電流。

HT7180是一款高功率非同步升壓轉換器,集成 22mΩ功率開關管,為便攜式系統提供高效的小尺寸解決方案。

PoE分離器則是將電源從以太網絡線分離,專門輸出電源給非PoE終端裝置。

第一代Type 1 PoE,定義為標準IEEE 802.3af,支持高達15.4W的功率預算,由PSE進行供電.之后的 802.3at Type-2標準,即PoE+,支持高達30W,且向下兼容Type 1 PD。

最新的802.3bt標準包括Type-3、PoE++(或UPoE)設備,最大功率預算為60W,以及100W Type-4設備。

這種配置大幅降低電纜中的功耗情況,使得更多的功率能夠到達 PD。此外還降低了允許的最小 PD 待機功率,提高對低能耗設計的支持。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

升壓值13V以下的DC-DC升壓應用需求,推廣一款集成10A開關管的12.8V輸出、大電流非同步DC-DC升壓IC:HT7180。

HT7180采用獨到的電路研發技術以及先進的半導體工藝制程,基于SOP8封裝,工作效率高達90%以上,無需外加散熱器,3.7V輸入升壓到12V,可穩定輸出2A電流。

HT7180是一款高功率非同步升壓轉換器,集成 22mΩ功率開關管,為便攜式系統提供高效的小尺寸解決方案。

PoE分離器則是將電源從以太網絡線分離,專門輸出電源給非PoE終端裝置。

第一代Type 1 PoE,定義為標準IEEE 802.3af,支持高達15.4W的功率預算,由PSE進行供電.之后的 802.3at Type-2標準,即PoE+,支持高達30W,且向下兼容Type 1 PD。

最新的802.3bt標準包括Type-3、PoE++(或UPoE)設備,最大功率預算為60W,以及100W Type-4設備。

這種配置大幅降低電纜中的功耗情況,使得更多的功率能夠到達 PD。此外還降低了允許的最小 PD 待機功率,提高對低能耗設計的支持。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607