幀長度檢測和SPI配置外部端需接電阻經受住-14V到6V電壓

發布時間:2022/1/19 12:35:17 訪問次數:1018

65納米線寬的Quad Data Rate (QDR) 和Double Data Rate (DDR) SRAM器件樣品。

新推出的72-Mbit QDRII、QDRII+、DDRII和DDRII+存儲器采用了賽普拉斯合作伙伴制造商 UMC 開發的工藝技術。

QDRII+和DDRII+器件具有片內終結電阻器 (ODT),消除了外部端需接電阻的要求,因而可提高信號的完整性,降低系統成本,節約板上空間。65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展35%,以幫助客戶縮短開發時間、節約開發成本。

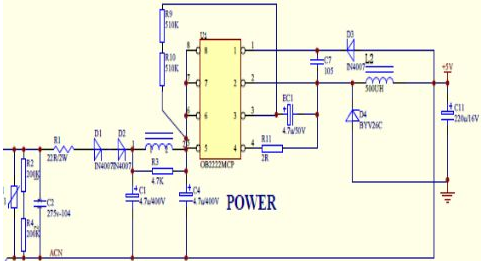

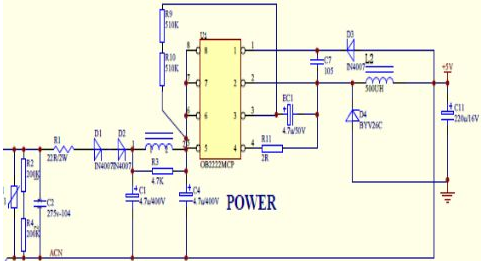

32位失調幀SPI從接口實現L9908和uC間通信,速率高達10MHz.SPI通信有5位CRC,1位幀計數器,幀長度檢測和SPI配置的視窗看門狗等安全保證.器件滿足AEC-Q100資質,完全和 ISO26262兼容, ASIL-D系統就緒.從VDD引腳的5V電壓產生3.3V內部電源.

工作在單12V系統,雙(24V系統)和48V電池應用,VDH馬達電源范圍從4.5V到75V.SPI可調整增益系數和輸出失調,內置了誤差校準,輸入檢測引腳能經受住-14V到6V電壓.

對于功率模塊晶圓,從長期供應安全考慮,比亞迪半導體采取自制晶圓為主,代工和外購為輔的整體策略,2018-2020年、2021年1-6月其晶圓產能利用率分別為78.61%、49.54%、32.33%和64.05%。

其他技術根本無法實現BrainChip解決方案可以提供的超低功耗自主、增量學習等特點。將這些芯片交到盡可能多的人手中是下一代人工智能成為現實的方式。BrainChip還將向系統集成商和開發人員提供完整的PCIe設計布局文件和材料清單 (BOM),使他們能夠構建自己的電路板并利用AKD1000芯片作為獨立嵌入式加速器或協處理器量產。

(素材來源:轉載自網絡,如涉版權請聯系刪除,特別感謝)

65納米線寬的Quad Data Rate (QDR) 和Double Data Rate (DDR) SRAM器件樣品。

新推出的72-Mbit QDRII、QDRII+、DDRII和DDRII+存儲器采用了賽普拉斯合作伙伴制造商 UMC 開發的工藝技術。

QDRII+和DDRII+器件具有片內終結電阻器 (ODT),消除了外部端需接電阻的要求,因而可提高信號的完整性,降低系統成本,節約板上空間。65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展35%,以幫助客戶縮短開發時間、節約開發成本。

32位失調幀SPI從接口實現L9908和uC間通信,速率高達10MHz.SPI通信有5位CRC,1位幀計數器,幀長度檢測和SPI配置的視窗看門狗等安全保證.器件滿足AEC-Q100資質,完全和 ISO26262兼容, ASIL-D系統就緒.從VDD引腳的5V電壓產生3.3V內部電源.

工作在單12V系統,雙(24V系統)和48V電池應用,VDH馬達電源范圍從4.5V到75V.SPI可調整增益系數和輸出失調,內置了誤差校準,輸入檢測引腳能經受住-14V到6V電壓.

對于功率模塊晶圓,從長期供應安全考慮,比亞迪半導體采取自制晶圓為主,代工和外購為輔的整體策略,2018-2020年、2021年1-6月其晶圓產能利用率分別為78.61%、49.54%、32.33%和64.05%。

其他技術根本無法實現BrainChip解決方案可以提供的超低功耗自主、增量學習等特點。將這些芯片交到盡可能多的人手中是下一代人工智能成為現實的方式。BrainChip還將向系統集成商和開發人員提供完整的PCIe設計布局文件和材料清單 (BOM),使他們能夠構建自己的電路板并利用AKD1000芯片作為獨立嵌入式加速器或協處理器量產。

(素材來源:轉載自網絡,如涉版權請聯系刪除,特別感謝)

公網安備44030402000607

公網安備44030402000607