555多諧振蕩器

發布時間:2013/4/13 16:46:16 訪問次數:8592

555時基電路是一種將模擬電路和數PIC12F629-I/P字電路結合在一起的混合集成電路,由于其具有寬范圍單電源電壓、可輸入模擬電平、輸出驅動功率較大、定時準確的特點,得到了廣泛的應用。

圖4-27所示電路圖中,IC1(555時基電路)構成多諧振蕩器。相對晶體管而言,用555時基電路構成多諧振瘍器,具有電路簡單、穩定可靠的特點。555多諧振蕩器工作原理分析如下。

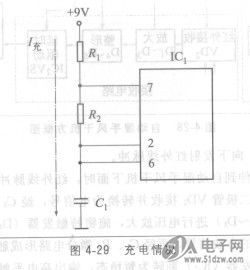

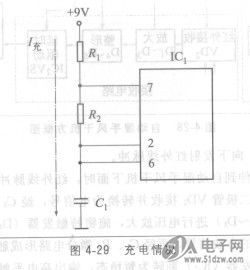

設起始時間Cl上無電壓,輸出端(第3腳)為“1”,+9V電源開始經Ri、R2向Cl充電,如圖4-29所示。

圖4-29 充電情況

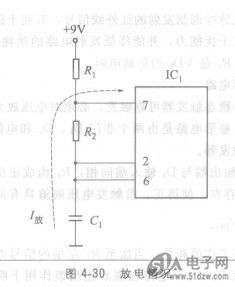

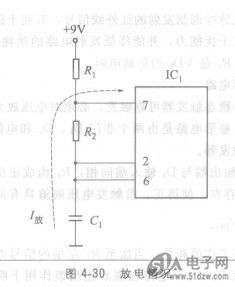

當Cl上電壓達到號VDD時,電路翻轉,輸出端(第3腳)變為“O”,同時放電端(第7腳)導通,Cl開始經Rz和第7腳放電,如圖4-30所示。

當Cl上電壓降至告VDD時,電路再次翻轉,輸出端(第3腳)變為“1”,同時放電端(第7腳)截止,C,又開始通過Ri、R2充電,如此周而復始形成振蕩。電路振蕩周期T≈O. 69(R1+2R2) Ci,振蕩頻率。改變R1、R2. Ci,即可改變振蕩頻率。改變Ri與R2的比值,可改變輸出方波的占空比。

555時基電路是一種將模擬電路和數PIC12F629-I/P字電路結合在一起的混合集成電路,由于其具有寬范圍單電源電壓、可輸入模擬電平、輸出驅動功率較大、定時準確的特點,得到了廣泛的應用。

圖4-27所示電路圖中,IC1(555時基電路)構成多諧振蕩器。相對晶體管而言,用555時基電路構成多諧振瘍器,具有電路簡單、穩定可靠的特點。555多諧振蕩器工作原理分析如下。

設起始時間Cl上無電壓,輸出端(第3腳)為“1”,+9V電源開始經Ri、R2向Cl充電,如圖4-29所示。

圖4-29 充電情況

當Cl上電壓達到號VDD時,電路翻轉,輸出端(第3腳)變為“O”,同時放電端(第7腳)導通,Cl開始經Rz和第7腳放電,如圖4-30所示。

當Cl上電壓降至告VDD時,電路再次翻轉,輸出端(第3腳)變為“1”,同時放電端(第7腳)截止,C,又開始通過Ri、R2充電,如此周而復始形成振蕩。電路振蕩周期T≈O. 69(R1+2R2) Ci,振蕩頻率。改變R1、R2. Ci,即可改變振蕩頻率。改變Ri與R2的比值,可改變輸出方波的占空比。

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607