右移位寄存器電路原理圖

發布時間:2013/5/10 20:17:41 訪問次數:3606

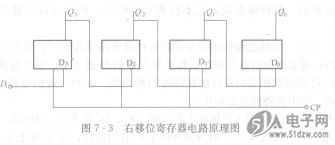

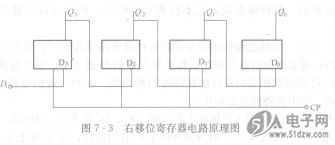

圖7-3是右移位寄存器電AD8057ARTZ-REEL路原理圖。它也是由四個D觸發器構成的,只是接法不同,而且輸入數據Di是加到左邊第一位的輸入端D上。

圖7-3右移位寄存器電路原理圖

根據前面的分析可知,當Di =1時,隨著時鐘脈沖而產生的逐步位移過程如下:

CP脈沖上升沿未到時,Q=OOOO

第一個脈沖上升沿到來時,Q=1000

第二個脈沖上升沿到來時,Q=1100

第三個脈沖上升沿到來時,Q一1110

第四個脈沖上升沿到來時,Q=ll11

由此可見,在右移寄存器中,每個時鐘脈沖都要把所儲存的各位向右移動一位。

除了左移寄存器和右移寄存器外,還有既能左移又能右移的雙向移位寄存器,它的工作原理大致上相同,只不過連接和控制的方法更為復雜一些,在此就不作介紹了。

移位寄存器的特點及常用型號

移位寄存器從邏輯結構上看,它有以下兩個特征:

(1)移位寄存器的位數是由寄存單元的個數決定。為了完成不同的移位功能,每個寄存單元的輸出與其相鄰的下一個寄存單元的輸入之間的連接方式也不同。

(2)所有寄存單元共用一個時鐘。在公共時鐘的作用下,各個寄存單元的工作是同步的。每輸入一個時鐘脈沖,寄存器的數據就順序向左或向右移動一位。

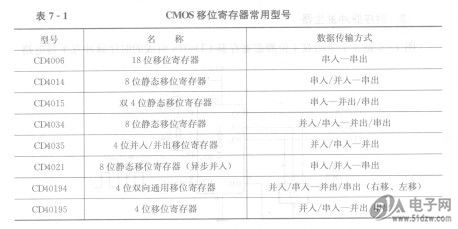

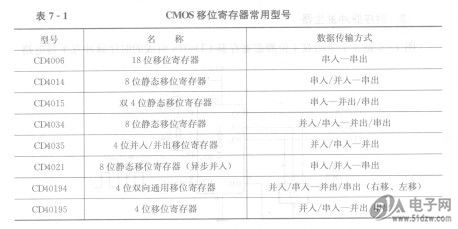

CMOS移位寄存器常用型號見表7-1。表7-1 CMOS移位寄存器常用型號

圖7-3是右移位寄存器電AD8057ARTZ-REEL路原理圖。它也是由四個D觸發器構成的,只是接法不同,而且輸入數據Di是加到左邊第一位的輸入端D上。

圖7-3右移位寄存器電路原理圖

根據前面的分析可知,當Di =1時,隨著時鐘脈沖而產生的逐步位移過程如下:

CP脈沖上升沿未到時,Q=OOOO

第一個脈沖上升沿到來時,Q=1000

第二個脈沖上升沿到來時,Q=1100

第三個脈沖上升沿到來時,Q一1110

第四個脈沖上升沿到來時,Q=ll11

由此可見,在右移寄存器中,每個時鐘脈沖都要把所儲存的各位向右移動一位。

除了左移寄存器和右移寄存器外,還有既能左移又能右移的雙向移位寄存器,它的工作原理大致上相同,只不過連接和控制的方法更為復雜一些,在此就不作介紹了。

移位寄存器的特點及常用型號

移位寄存器從邏輯結構上看,它有以下兩個特征:

(1)移位寄存器的位數是由寄存單元的個數決定。為了完成不同的移位功能,每個寄存單元的輸出與其相鄰的下一個寄存單元的輸入之間的連接方式也不同。

(2)所有寄存單元共用一個時鐘。在公共時鐘的作用下,各個寄存單元的工作是同步的。每輸入一個時鐘脈沖,寄存器的數據就順序向左或向右移動一位。

CMOS移位寄存器常用型號見表7-1。表7-1 CMOS移位寄存器常用型號

上一篇:移位寄存器的結構及工作原理

上一篇:時序脈沖發生器

公網安備44030402000607

公網安備44030402000607