P型溝道MOSFET晶體管俯視圖

發布時間:2013/7/29 21:02:08 訪問次數:2254

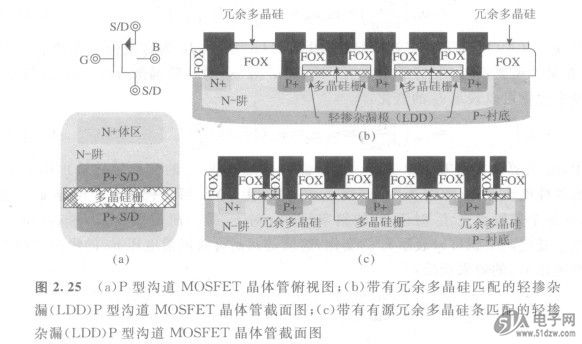

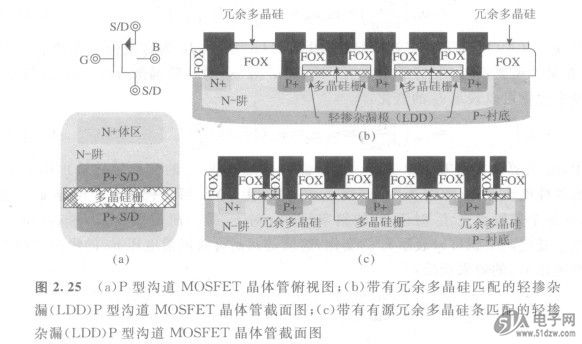

把MOS器件靠近同向放置,具有共同的質心、交叉耦合并且在其周圍放置冗余器件,可以減弱多晶硅光刻誤差帶來的影響,進而提高器件的匹配性能。PI5A100QEX柵極必須延伸到漏極和源極寬度之外,以保證溝道在器件寬度上完全反犁,如圖2.25(a)所示。當體極和源極具有相同電勢,N+體區通常會緊靠P+源區或者漏區,強迫后者為源極。

為了節省空間,減小多晶硅光刻誤差,可能使用冗余多晶硅條代替冗余晶體管。當這些薄氧化區域在多晶硅柵下大約450A量級時,這些多晶硅條可以很好地實現匹配的功能。但是在現代先進工藝中,氧化物區域在125 A量級甚至更小,可以在它們周邊冗余多晶硅條下放置有源多晶硅柵[圖2.25(b)],減小多晶硅條光刻誤差的大小。在厚的場氧(FOX)上自動放置平坦的多晶硅條可以降低其到硅襯底上的寄生電容。因此使用冗余晶體管代替平坦的冗余多晶硅條并且將其偏置在截止區域,或者采用有源冗余多晶硅柵條,如圖2.25(c)所示,這樣的效果是最好的。有源冗余多晶硅條可能會形成寄生的MOS晶體管,因此應合理放置,并且應使其處于合理的偏置狀態,防止它們下面的溝道反型。例如,N-阱區域上的有源冗余多晶硅條應該連接到正的電勢上,使其區域下積累多數N型電荷載流子。

在氧化層較薄的情況下,漏極區域附近的電場強度會增加(即漏柵電壓較大,而電介質厚度相對較薄),這會提前引發碰撞電離和熱載流子效應,從而影響器件的可靠性。為了防止這些情況發生,采用輕摻雜漏(LDD)區域來擴展漏區,如圖2.25 (b)和圖2.25(c)所示,可以降低電荷載流子濃度,從而降低柵氧化層出現熱載流子效應的可能性。類似地,采用更輕擴散阱區代替高濃度擴散的漏區,可以增加漏極體極的擊穿電壓——有時這些器件也稱為漏區擴展晶體管。

把MOS器件靠近同向放置,具有共同的質心、交叉耦合并且在其周圍放置冗余器件,可以減弱多晶硅光刻誤差帶來的影響,進而提高器件的匹配性能。PI5A100QEX柵極必須延伸到漏極和源極寬度之外,以保證溝道在器件寬度上完全反犁,如圖2.25(a)所示。當體極和源極具有相同電勢,N+體區通常會緊靠P+源區或者漏區,強迫后者為源極。

為了節省空間,減小多晶硅光刻誤差,可能使用冗余多晶硅條代替冗余晶體管。當這些薄氧化區域在多晶硅柵下大約450A量級時,這些多晶硅條可以很好地實現匹配的功能。但是在現代先進工藝中,氧化物區域在125 A量級甚至更小,可以在它們周邊冗余多晶硅條下放置有源多晶硅柵[圖2.25(b)],減小多晶硅條光刻誤差的大小。在厚的場氧(FOX)上自動放置平坦的多晶硅條可以降低其到硅襯底上的寄生電容。因此使用冗余晶體管代替平坦的冗余多晶硅條并且將其偏置在截止區域,或者采用有源冗余多晶硅柵條,如圖2.25(c)所示,這樣的效果是最好的。有源冗余多晶硅條可能會形成寄生的MOS晶體管,因此應合理放置,并且應使其處于合理的偏置狀態,防止它們下面的溝道反型。例如,N-阱區域上的有源冗余多晶硅條應該連接到正的電勢上,使其區域下積累多數N型電荷載流子。

在氧化層較薄的情況下,漏極區域附近的電場強度會增加(即漏柵電壓較大,而電介質厚度相對較薄),這會提前引發碰撞電離和熱載流子效應,從而影響器件的可靠性。為了防止這些情況發生,采用輕摻雜漏(LDD)區域來擴展漏區,如圖2.25 (b)和圖2.25(c)所示,可以降低電荷載流子濃度,從而降低柵氧化層出現熱載流子效應的可能性。類似地,采用更輕擴散阱區代替高濃度擴散的漏區,可以增加漏極體極的擊穿電壓——有時這些器件也稱為漏區擴展晶體管。

上一篇:不同MOSFETI作區的柵源電容和柵漏電容的變化情況

上一篇:本征器件

熱門點擊

熱門點擊

- 容抗、感抗與頻率的關系

- SRPP電路工作點的選定

- 集成電路TA7630P引腳作用

- 輸出耦合電容值的選取

- 束射四極管與五極管

- P型溝道MOSFET晶體管俯視圖

- 反饋公式

- VD2和VD3兩只整流二極管導通時的電流回路

- 采用開關集成電路和繼電器構成的揚聲器保護電路

- 電容器的阻抗隨信號頻率變化的基本工作特性

推薦技術資料

推薦技術資料

- 自制智能型ICL7135

- 表頭使ff11CL7135作為ADC,ICL7135是... [詳細]

公網安備44030402000607

公網安備44030402000607