可編程陣列邏輯(PAL)

發布時間:2013/10/21 20:01:31 訪問次數:2543

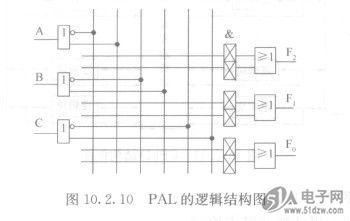

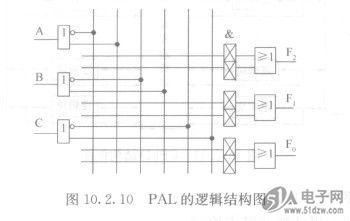

PAL由一個可編程的與陣列和固定連接的或陣列組成。HA17902圖10.2.10所示為i輸入i輸出PAL的邏輯結構圖。

圖10.2.10 PAL的邏輯結構圖

PAL器件的結構是由生產廠家固定的,從PAL問世至今,大約已生產出幾十種不同的產品,按其輸出和反饋結構可分為5種基本類型:專用輸出的基本門陣列結構、帶反饋的可編程I/O結構、帶反饋的寄存輸出結構、加異或帶反饋的寄存輸出結構、算術選通反饋結構。

通用陣列邏輯( GAL)

GAI。是1985年開發出來的一種新的PLD器件,它是在PAL器件的基礎上綜合了E2 PROM和CMOS技術發展起來的。GAL器件具有PAL器件所沒有的可擦除、可重新編程及其結構可組的特點。

通用型GAI。包括GAI.16V8和GAI。20V8兩種器件。其中GAI。16V8是20腳器件,器件型號中的16表示最多有16個引腳作為輸入端,器件型號中的8表示器件內有8個OI.MC(輸出邏輯宏單元),最多有8個引腳作為輸出端。同理,GAL20V8的最大輸入引腳數是20,GAI。20V8是24腳器件。

GAI。器件按其門陣列的可編程結構哥分為兩大類:一類是與PAL基本結構相似的普通型GAL器件,其與門陣列是可編程的,或門陣列是固定連接的;另一類是與PLA器件相似的新一代GAI。器件。

此外,還有復雜的可編程邏輯器件(CPLD)、現場可編程門陣列(FPGA)等,CPLD具有“在系統可編程”(ISP)特性,它們在應用時需要專門的開發軟件,如ISP Synario等進行設計分析。可編程器件CPLD/FPGA生產廠商眾多,比較知名的有Altera、Lattice、Xilinx和Actel公司等,上述幾家公司推出的芯片均配有功能強大的開發軟件,能支持多種電路設計方法,如硬件描述語言(VHDL)等,使用方便。

復雜可編程邏輯器件( CPLD)

前面所介紹到的可編程邏輯器件都屬于簡單的PLD。隨著微電子技術的發展和應用上的需求提高,簡單PLD在集成度和性能方面難以滿足要求,因此集成度更高、功能更強的復雜可編程器件(CPI。D)便迅速發展起來。

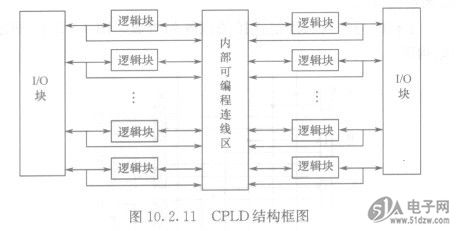

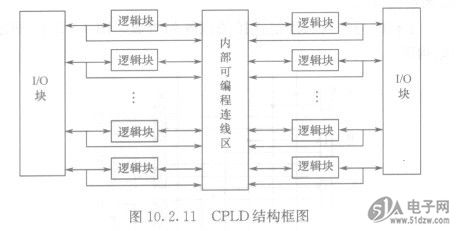

高集成度的CPI.D具有更多的輸入信號、更多的乘積項和更多的宏單元。盡管各廠商生產的CPLD器件結構千差萬別,但它們仍有共同之處,一般CPLD的結構框圖如圖10.2.11所示。其中邏輯塊就相當于~個GAL器件,CPLD中有多個邏輯塊,這些邏輯塊之間可以使用可編程內部連線實現相互連接。為了增強對I/O的控制力,提高引腳的適應性,CPI。D中還增加了I/O控制塊。每個I/O塊中有若干個I/O單元。

PAL由一個可編程的與陣列和固定連接的或陣列組成。HA17902圖10.2.10所示為i輸入i輸出PAL的邏輯結構圖。

圖10.2.10 PAL的邏輯結構圖

PAL器件的結構是由生產廠家固定的,從PAL問世至今,大約已生產出幾十種不同的產品,按其輸出和反饋結構可分為5種基本類型:專用輸出的基本門陣列結構、帶反饋的可編程I/O結構、帶反饋的寄存輸出結構、加異或帶反饋的寄存輸出結構、算術選通反饋結構。

通用陣列邏輯( GAL)

GAI。是1985年開發出來的一種新的PLD器件,它是在PAL器件的基礎上綜合了E2 PROM和CMOS技術發展起來的。GAL器件具有PAL器件所沒有的可擦除、可重新編程及其結構可組的特點。

通用型GAI。包括GAI.16V8和GAI。20V8兩種器件。其中GAI。16V8是20腳器件,器件型號中的16表示最多有16個引腳作為輸入端,器件型號中的8表示器件內有8個OI.MC(輸出邏輯宏單元),最多有8個引腳作為輸出端。同理,GAL20V8的最大輸入引腳數是20,GAI。20V8是24腳器件。

GAI。器件按其門陣列的可編程結構哥分為兩大類:一類是與PAL基本結構相似的普通型GAL器件,其與門陣列是可編程的,或門陣列是固定連接的;另一類是與PLA器件相似的新一代GAI。器件。

此外,還有復雜的可編程邏輯器件(CPLD)、現場可編程門陣列(FPGA)等,CPLD具有“在系統可編程”(ISP)特性,它們在應用時需要專門的開發軟件,如ISP Synario等進行設計分析。可編程器件CPLD/FPGA生產廠商眾多,比較知名的有Altera、Lattice、Xilinx和Actel公司等,上述幾家公司推出的芯片均配有功能強大的開發軟件,能支持多種電路設計方法,如硬件描述語言(VHDL)等,使用方便。

復雜可編程邏輯器件( CPLD)

前面所介紹到的可編程邏輯器件都屬于簡單的PLD。隨著微電子技術的發展和應用上的需求提高,簡單PLD在集成度和性能方面難以滿足要求,因此集成度更高、功能更強的復雜可編程器件(CPI。D)便迅速發展起來。

高集成度的CPI.D具有更多的輸入信號、更多的乘積項和更多的宏單元。盡管各廠商生產的CPLD器件結構千差萬別,但它們仍有共同之處,一般CPLD的結構框圖如圖10.2.11所示。其中邏輯塊就相當于~個GAL器件,CPLD中有多個邏輯塊,這些邏輯塊之間可以使用可編程內部連線實現相互連接。為了增強對I/O的控制力,提高引腳的適應性,CPI。D中還增加了I/O控制塊。每個I/O塊中有若干個I/O單元。

上一篇:可編程邏輯陣列(PLA)

上一篇:FPGA中實現邏輯功能的基本原理

熱門點擊

熱門點擊

- 常小數點的七段共陰極半導體數碼管BS201的

- 由3AD18型功率管組成的乙類推挽功率放大器

- 常見的BCD編碼

- 量化和編碼

- 七段字形譯碼器

- 吸錫電烙鐵的外形與結構

- 可變電容器及其主要參數

- 銼削平面的方法

- 三種類型電位器阻值變化特性

- 設計總結報告的評分標準

推薦技術資料

推薦技術資料

- 自制經典的1875功放

- 平時我也經常逛一些音響DIY論壇,發現有很多人喜歡LM... [詳細]

公網安備44030402000607

公網安備44030402000607