實驗步驟

發布時間:2014/1/12 16:07:02 訪問次數:784

①在Max+ plusⅡ10.2軟件中新建原理圖文件,輸入自XDM8107AAR11己設計的原理圖,編譯,仿真,鎖定管腳并下載到目標芯片。

②對于實驗內容1、2,將信號源模塊第一全局時鐘GCLK1跳線器接需要的計數頻率(最低位計數頻率),第二全局時鐘GCLK2跳線器接32768 Hz,觀察數碼管SMl-SM8是否按要求顯示計數結果,特別是進位時的情況。

③總結同步計數器與異步計數器的區別。

5.3.3 MAX+plusⅡ實驗平臺上的數字電路實驗—一實驗2:基本組合邏輯電路的VHDL模型

(1)實驗目的

①掌握簡單的VHDL程序設計。

②掌握用VHDL對基本組合邏輯電路的建模。

(2)實驗內容

分別設計并實現緩沖器、選擇器、譯碼器、編碼器,移位器。

(3)實驗儀器

ZY11EDA13BE型實驗箱通用編程模塊,配置模塊,開關按鍵模塊,LED顯示模塊。

(4)實驗原理

三態緩沖器

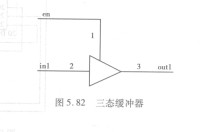

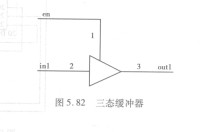

三態緩沖器( Tri-state Buffer)的作用是轉換數據、增強驅動能力以及把功能模塊與總線相連接。在使用總線互連方式時,與總線通信的器件通常要通過三態緩沖器與總線相連。如果緩沖器的使能端en為1,則緩沖器的輸入端inl的信號值被復制到輸出端;如果緩沖器的使能端en為其他數值,則緩沖器的輸出端為高阻態。三態緩沖器的輸出端可以用線與的方式和其他緩沖器的輸出端接在一起。三態緩沖器的VHDL源代碼模型如下(見圖5.82):

①在Max+ plusⅡ10.2軟件中新建原理圖文件,輸入自XDM8107AAR11己設計的原理圖,編譯,仿真,鎖定管腳并下載到目標芯片。

②對于實驗內容1、2,將信號源模塊第一全局時鐘GCLK1跳線器接需要的計數頻率(最低位計數頻率),第二全局時鐘GCLK2跳線器接32768 Hz,觀察數碼管SMl-SM8是否按要求顯示計數結果,特別是進位時的情況。

③總結同步計數器與異步計數器的區別。

5.3.3 MAX+plusⅡ實驗平臺上的數字電路實驗—一實驗2:基本組合邏輯電路的VHDL模型

(1)實驗目的

①掌握簡單的VHDL程序設計。

②掌握用VHDL對基本組合邏輯電路的建模。

(2)實驗內容

分別設計并實現緩沖器、選擇器、譯碼器、編碼器,移位器。

(3)實驗儀器

ZY11EDA13BE型實驗箱通用編程模塊,配置模塊,開關按鍵模塊,LED顯示模塊。

(4)實驗原理

三態緩沖器

三態緩沖器( Tri-state Buffer)的作用是轉換數據、增強驅動能力以及把功能模塊與總線相連接。在使用總線互連方式時,與總線通信的器件通常要通過三態緩沖器與總線相連。如果緩沖器的使能端en為1,則緩沖器的輸入端inl的信號值被復制到輸出端;如果緩沖器的使能端en為其他數值,則緩沖器的輸出端為高阻態。三態緩沖器的輸出端可以用線與的方式和其他緩沖器的輸出端接在一起。三態緩沖器的VHDL源代碼模型如下(見圖5.82):

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607