譯碼器

發布時間:2014/7/12 13:37:24 訪問次數:1589

譯碼器分兩大類,一類是通用譯碼器,另一類是顯示譯碼器,本實驗僅介紹前者。

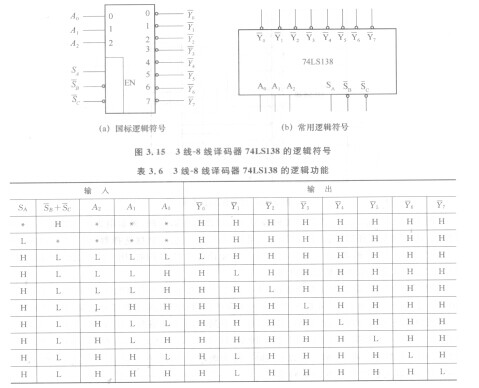

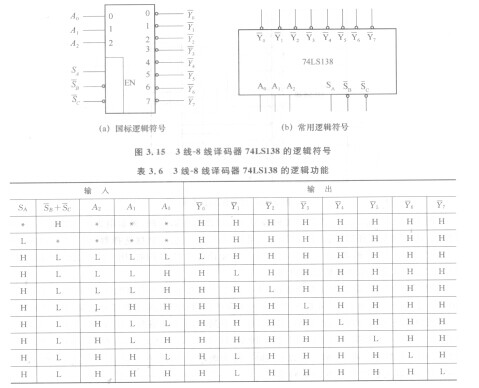

74LS138是3線一8線譯碼器,XC2064-70PC68C是一種通用譯碼器,其邏輯符號如圖3.15所示,其功能如表3.6所示。其申,A。、A.、A。是地址輸入端,y。、Yl、…、y,是譯碼輸出端,SA、S。、虧。是使能端,僅當SA、SB、SC分別為H、L、L時,譯碼器才正常譯碼;否則,譯碼器不實現譯碼,這時不管譯碼輸入A2、Ai、A。為何值,8個譯碼輸出y。、Yl、…、y,都輸出高電平。3線一8線譯碼器實際上也是一個負脈沖輸出的脈沖分配器。如利用使能端中的一個輸入端輸入數據信息,器件就成為數據分配器。例如,若從SA輸入端輸人數據信息,SB—SC =0,地址碼所對應的輸出是SA數據信息的反碼;若從SB輸入端輸入數據信息,SA =1,Sc =0,地址碼所對應的輸出就是數據信息Sn。 .

譯碼器的每一路輸出,實際上是各地址變量組成函數的一個最小項的反變量,利用其中一部分輸出端輸出的與非關系,也就是它們相應最小項的或邏輯表達式,能方便地實現邏輯函數。

例如,用3線-8線譯碼器實現全加器的勸能。設A。和B。分別是被加數和加數,C。是低位向本位的進位,C。+,是本位向高位的進位,S。是和數。全加器的邏輯表達式為Sn =An B,, C,,+AnB,, C,,+An BnCn +AnBnCn= Yi +Y2+Y4+Yr =Y, Y2 Y4 Y7

Cn+.一A.B.C.+A.B.C.+A.B.C.+A.B.C.=Y3+Y5十Y6+Y7=Y3 Y5 Y6 y,上列表達式可用如圖3. 16所示的電路來實現。

用MSI組合功能件設計組合電路的基本步驟同用小規模集成電路(SSI)設計的步驟,只是邏輯表達式應該表示成類似于所選用的MSI組合功能件的輸出/輸入的標準邏輯表達式,以便很方便地應用所選用的MSI組合功能件實現實際問題所要求的邏輯功能。

譯碼器分兩大類,一類是通用譯碼器,另一類是顯示譯碼器,本實驗僅介紹前者。

74LS138是3線一8線譯碼器,XC2064-70PC68C是一種通用譯碼器,其邏輯符號如圖3.15所示,其功能如表3.6所示。其申,A。、A.、A。是地址輸入端,y。、Yl、…、y,是譯碼輸出端,SA、S。、虧。是使能端,僅當SA、SB、SC分別為H、L、L時,譯碼器才正常譯碼;否則,譯碼器不實現譯碼,這時不管譯碼輸入A2、Ai、A。為何值,8個譯碼輸出y。、Yl、…、y,都輸出高電平。3線一8線譯碼器實際上也是一個負脈沖輸出的脈沖分配器。如利用使能端中的一個輸入端輸入數據信息,器件就成為數據分配器。例如,若從SA輸入端輸人數據信息,SB—SC =0,地址碼所對應的輸出是SA數據信息的反碼;若從SB輸入端輸入數據信息,SA =1,Sc =0,地址碼所對應的輸出就是數據信息Sn。 .

譯碼器的每一路輸出,實際上是各地址變量組成函數的一個最小項的反變量,利用其中一部分輸出端輸出的與非關系,也就是它們相應最小項的或邏輯表達式,能方便地實現邏輯函數。

例如,用3線-8線譯碼器實現全加器的勸能。設A。和B。分別是被加數和加數,C。是低位向本位的進位,C。+,是本位向高位的進位,S。是和數。全加器的邏輯表達式為Sn =An B,, C,,+AnB,, C,,+An BnCn +AnBnCn= Yi +Y2+Y4+Yr =Y, Y2 Y4 Y7

Cn+.一A.B.C.+A.B.C.+A.B.C.+A.B.C.=Y3+Y5十Y6+Y7=Y3 Y5 Y6 y,上列表達式可用如圖3. 16所示的電路來實現。

用MSI組合功能件設計組合電路的基本步驟同用小規模集成電路(SSI)設計的步驟,只是邏輯表達式應該表示成類似于所選用的MSI組合功能件的輸出/輸入的標準邏輯表達式,以便很方便地應用所選用的MSI組合功能件實現實際問題所要求的邏輯功能。

上一篇:MSI組合功能件的應用

公網安備44030402000607

公網安備44030402000607