數字電路的負載能力

發布時間:2014/11/19 18:45:58 訪問次數:1623

在數字集成電路芯片的使用中, HER606應注意到它們的驅動能力及不用輸入端的處理。如果某一數字電路接的負載太多,超出了它的負載能力,其工作必定不可靠。數字電路輸入及輸出引線應盡可能短,平行走向的引線不要太長,以減小沖擊電流的影響 。

在TTL電路中,遇到容性負載時要特別小心,因為容性負載會使下一級輸入波形邊沿變慢,而緩慢邊沿輸入會在數字電路狀態變換過程中產生幅度較大的振蕩,形成一個干擾源。遇到這種情況,可以利用施密特觸發器首先對波形進行整形,然后再送到下一級電路。也可以利用DTL電路來處理容性負載的輸出,它不會因為前沿慢而產生振蕩。

同樣,在遇到感性負載時,在電流關斷瞬間會產生很高的感應電壓,它會使電路元器件擊穿,從而產生干擾,因此必須加以克服。通常可以在電感負載上并聯保護二極管或電阻和電容。

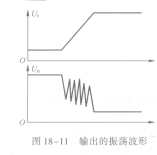

對于CMOS屯路來說,同樣存在TTL電路中出現的問題。若輸入信號在CMOS的轉換特性的過渡段里產生波動,則在其輸出端必然會出現振蕩,其原因是過渡段具有放大倍數很大的放大特性,如圖18 - 11所示。

根據圖18 - 11所示的波形可以想到,數字電路的輸出端出現振蕩的原因是輸入信號變化太慢,尤其是在過渡過程中由電源或其他途徑混入電壓波動。當輸入電壓的過渡時間大于1¨s時,這種輸出振蕩就會產生。

克服這種干擾的方法是減小輸入電壓的過渡時間,更有效的方法就是采用施密特電路。

在電路設計中可能會遇到這樣的情況:要獲得的信號必須經過一段很惡劣的干擾環境才能到達信號的輸入端,而信號源在這段惡劣環境中會耦合比信號本身還大的干擾,使系統無法正常工作。為了克服干擾的影響,可以在信號源處先對信號進行放大使信號幅度足夠大;在目的地的輸入端再進行衰減。例如,SV的信號首先被放大到100V,傳輸后再衰減為5V。那么,即使干擾環境造成2V的干擾,經衰減也就微不足道了。

施密特觸發器的輸入和輸出具有滯后特性。利用這種特性,可以對輸入端的干擾產生較好的抑制。在設計電路時,遇到干擾比較大的地方,可以采用這種電路。

對于幅度大而持續時間短的干擾,在電路中可以利用低通濾波器進行濾除。因為這種于擾的頻率比信號的頻率高,簡單的RC低通濾波器就能奏效。

在數字集成電路芯片的使用中, HER606應注意到它們的驅動能力及不用輸入端的處理。如果某一數字電路接的負載太多,超出了它的負載能力,其工作必定不可靠。數字電路輸入及輸出引線應盡可能短,平行走向的引線不要太長,以減小沖擊電流的影響 。

在TTL電路中,遇到容性負載時要特別小心,因為容性負載會使下一級輸入波形邊沿變慢,而緩慢邊沿輸入會在數字電路狀態變換過程中產生幅度較大的振蕩,形成一個干擾源。遇到這種情況,可以利用施密特觸發器首先對波形進行整形,然后再送到下一級電路。也可以利用DTL電路來處理容性負載的輸出,它不會因為前沿慢而產生振蕩。

同樣,在遇到感性負載時,在電流關斷瞬間會產生很高的感應電壓,它會使電路元器件擊穿,從而產生干擾,因此必須加以克服。通常可以在電感負載上并聯保護二極管或電阻和電容。

對于CMOS屯路來說,同樣存在TTL電路中出現的問題。若輸入信號在CMOS的轉換特性的過渡段里產生波動,則在其輸出端必然會出現振蕩,其原因是過渡段具有放大倍數很大的放大特性,如圖18 - 11所示。

根據圖18 - 11所示的波形可以想到,數字電路的輸出端出現振蕩的原因是輸入信號變化太慢,尤其是在過渡過程中由電源或其他途徑混入電壓波動。當輸入電壓的過渡時間大于1¨s時,這種輸出振蕩就會產生。

克服這種干擾的方法是減小輸入電壓的過渡時間,更有效的方法就是采用施密特電路。

在電路設計中可能會遇到這樣的情況:要獲得的信號必須經過一段很惡劣的干擾環境才能到達信號的輸入端,而信號源在這段惡劣環境中會耦合比信號本身還大的干擾,使系統無法正常工作。為了克服干擾的影響,可以在信號源處先對信號進行放大使信號幅度足夠大;在目的地的輸入端再進行衰減。例如,SV的信號首先被放大到100V,傳輸后再衰減為5V。那么,即使干擾環境造成2V的干擾,經衰減也就微不足道了。

施密特觸發器的輸入和輸出具有滯后特性。利用這種特性,可以對輸入端的干擾產生較好的抑制。在設計電路時,遇到干擾比較大的地方,可以采用這種電路。

對于幅度大而持續時間短的干擾,在電路中可以利用低通濾波器進行濾除。因為這種于擾的頻率比信號的頻率高,簡單的RC低通濾波器就能奏效。

上一篇:數字電路的抗干擾設計

上一篇:數字電路輸入端的抗干擾措施

公網安備44030402000607

公網安備44030402000607