UC2002 表征門電路開關速度的參數

發布時間:2020/2/9 11:42:03 訪問次數:8148

表3.11 幾種cmos電路的電源電壓值,目前使用的兩種雙極型數字集成電路是ttl和ecl系列。ttl是應用最早,技術比較成熟的集成電路,曾被廣泛使用。大規模集成電路的發展要求每個邏輯單元電路的結構簡單,并且功耗低。ttl電路不能滿足這個條件,因此逐漸被cmos電路取代,退出其主導地位。由于ttl技術在整個數字集成電路設計領域中的歷史地位和影響,很多數字系統設計技術仍采用ttl技術,特別是從小規模到中規模數字系統的集成,因此推出了新型的低功耗和高速ttl器件,這種新型的ttl使用肖特基勢壘二極管(bsd①),以避免bjt工作在飽和狀態,從而提高工作速度。

最早的ttl門電路是74系列。后來出現了改進型的74h系列,其工作速度提高了,但功耗卻增加了。而74l系列的功耗降低了很多,但工作速度也降低了。為了解決功耗和速度之間的矛盾,推出了低功耗和高速的74s系列,它使用肖特基晶體三極管,使電路的工作速度和功耗均得到改善。之后又生產出74ls系列,其速度與74系列相當,但功耗卻降低到74系列的寧3 74ls系列廣泛應用于中、小規模集成電路。隨著集成電路的發展,生產出進一步改進的ttl系列被廣泛使用。ecl電路主要用于高速或超高速數字系統或設各中.砷化鎵是繼鍺和硅之后發展起來的新一代半導體材料。由于砷化鎵器件中1bsd系schottkibarricrodiodc的縮寫。

參數電源電壓范圍v/v,電源最大電壓額定值w/Ⅴ種噪聲的干擾,例如信號傳輸引起的噪聲,信號的高低電平轉換引起的噪聲,

或者鄰近開關信號所引起的隨機脈沖的噪聲。這些噪聲會疊加在工作信號上,只要其幅度不超過邏輯電平允許的最小值或最大值,則輸出邏輯狀態不會受影響。通常將這個最大噪聲幅度稱為噪聲容限。電路的噪聲容限愈大,其抗干擾能力愈強。

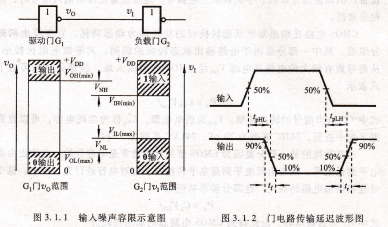

圖3.1.1所示為噪聲容限定義的示意圖。前一級驅動門電路的輸出,就是后一級負載門電路的輸人。當前一級輸出高電平的最小值仍能滿足后級高電平輸人最小值時,輸人高電平的噪聲容限為

7nh=oh(min)ah(nal-n) (3.1.1)

同理得出,輸人低電平的噪聲容限

ynl=y1+max)lol(max) (3.1.2)

根據74hc系列cmos集成電路在5v典型工作電壓時的參數,求得其輸人高、低電平的噪聲容限分別為:

高電平的噪聲容限 ynh=yon(min)uym(min)=4.9v-3.5v=1.4v

低電平的噪聲容限 ul=uil(m ax)yomax)=1.5Ⅴ-0.1Ⅴ=1.4v

其他cmos系列的高、低電平的噪聲容限列于表3.1.2中,驅動門g1負載門g2.

圖3.1.1 輸人噪聲容限示意圖 圖3.1.2 門電路傳輸延遲波形圖

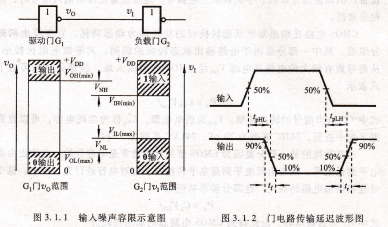

傳輸延遲時間,傳輸延遲時間是表征門電路開關速度的參數,它說明門電路在輸入脈沖波形的作用下,其輸出波形相對于輸入波形延遲了多長的時間。當門電路的輸人端加人一脈沖波形,其相應的輸出波形如圖3.1.2所示。通常輸出波形下降沿、上升沿的中點與輸入波形對應沿中點之間的時間間隔,分別用tplh和jphl,輸出mos邏輯閘電路.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

表3.11 幾種cmos電路的電源電壓值,目前使用的兩種雙極型數字集成電路是ttl和ecl系列。ttl是應用最早,技術比較成熟的集成電路,曾被廣泛使用。大規模集成電路的發展要求每個邏輯單元電路的結構簡單,并且功耗低。ttl電路不能滿足這個條件,因此逐漸被cmos電路取代,退出其主導地位。由于ttl技術在整個數字集成電路設計領域中的歷史地位和影響,很多數字系統設計技術仍采用ttl技術,特別是從小規模到中規模數字系統的集成,因此推出了新型的低功耗和高速ttl器件,這種新型的ttl使用肖特基勢壘二極管(bsd①),以避免bjt工作在飽和狀態,從而提高工作速度。

最早的ttl門電路是74系列。后來出現了改進型的74h系列,其工作速度提高了,但功耗卻增加了。而74l系列的功耗降低了很多,但工作速度也降低了。為了解決功耗和速度之間的矛盾,推出了低功耗和高速的74s系列,它使用肖特基晶體三極管,使電路的工作速度和功耗均得到改善。之后又生產出74ls系列,其速度與74系列相當,但功耗卻降低到74系列的寧3 74ls系列廣泛應用于中、小規模集成電路。隨著集成電路的發展,生產出進一步改進的ttl系列被廣泛使用。ecl電路主要用于高速或超高速數字系統或設各中.砷化鎵是繼鍺和硅之后發展起來的新一代半導體材料。由于砷化鎵器件中1bsd系schottkibarricrodiodc的縮寫。

參數電源電壓范圍v/v,電源最大電壓額定值w/Ⅴ種噪聲的干擾,例如信號傳輸引起的噪聲,信號的高低電平轉換引起的噪聲,

或者鄰近開關信號所引起的隨機脈沖的噪聲。這些噪聲會疊加在工作信號上,只要其幅度不超過邏輯電平允許的最小值或最大值,則輸出邏輯狀態不會受影響。通常將這個最大噪聲幅度稱為噪聲容限。電路的噪聲容限愈大,其抗干擾能力愈強。

圖3.1.1所示為噪聲容限定義的示意圖。前一級驅動門電路的輸出,就是后一級負載門電路的輸人。當前一級輸出高電平的最小值仍能滿足后級高電平輸人最小值時,輸人高電平的噪聲容限為

7nh=oh(min)ah(nal-n) (3.1.1)

同理得出,輸人低電平的噪聲容限

ynl=y1+max)lol(max) (3.1.2)

根據74hc系列cmos集成電路在5v典型工作電壓時的參數,求得其輸人高、低電平的噪聲容限分別為:

高電平的噪聲容限 ynh=yon(min)uym(min)=4.9v-3.5v=1.4v

低電平的噪聲容限 ul=uil(m ax)yomax)=1.5Ⅴ-0.1Ⅴ=1.4v

其他cmos系列的高、低電平的噪聲容限列于表3.1.2中,驅動門g1負載門g2.

圖3.1.1 輸人噪聲容限示意圖 圖3.1.2 門電路傳輸延遲波形圖

傳輸延遲時間,傳輸延遲時間是表征門電路開關速度的參數,它說明門電路在輸入脈沖波形的作用下,其輸出波形相對于輸入波形延遲了多長的時間。當門電路的輸人端加人一脈沖波形,其相應的輸出波形如圖3.1.2所示。通常輸出波形下降沿、上升沿的中點與輸入波形對應沿中點之間的時間間隔,分別用tplh和jphl,輸出mos邏輯閘電路.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

熱門點擊

熱門點擊

- LT1510IG 數值比較器的位數擴展

- IRF1405 真值表的內容填人四變量卡諾圖

- LM2936BM-5.0 功率變換組件的三部分

- XCR3384XL-10FG324I 變壓器鐵芯有卷環E型和卷環Y型

- TM200RZ-24(2H) 發電機負載勵磁特性發電機空載

- RL1004-2910-97-D1 JFET的變壓器反饋式IC振蕩電路

- MAX3832UCB-D 匯流條短路故障及逆序保護

- MPC9352AC 電路輸出管的漏極和電源

- UC2002 表征門電路開關速度的參數

- SST39VF3201-70 轉換式觸點式舌簧管繼電器

推薦電子資訊

推薦電子資訊

- 2013中國醫療電子展覽會

- v\:* {behavior:url(#def... [詳細]

公網安備44030402000607

公網安備44030402000607